# Real-Time Clock and Interrupt Module (RCIM) User's Guide

0898007-400 June 2008 Copyright 2008 by Concurrent Computer Corporation. All rights reserved. This publication or any part thereof is intended for use with Concurrent Computer Corporation products by Concurrent Computer Corporation personnel, customers, and end–users. It may not be reproduced in any form without the written permission of the publisher.

The information contained in this document is believed to be correct at the time of publication. It is subject to change without notice. Concurrent Computer Corporation makes no warranties, expressed or implied, concerning the information contained in this document.

To report an error or comment on a specific portion of the manual, photocopy the page in question and mark the correction or comment on the copy. Mail the copy (and any additional comments) to Concurrent Computer Corporation, 2881 Gateway Drive Pompano Beach, FL 33069. Mark the envelope "Attention: Real-Time OS Publications **Department**." This publication may not be reproduced for any other reason in any form without written permission of the publisher.

Concurrent Computer Corporation and its logo are registered trademarks of Concurrent Computer Corporation. All other Concurrent product names are trademarks of Concurrent while all other product names are trademarks or registered trademarks of their respective owners. Linux® is used pursuant to a sublicense from the Linux Mark Institute.

#### Printed in U. S. A.

| Revision History:              | Level: | Effective With:               |

|--------------------------------|--------|-------------------------------|

| Original Release August 2002   | 000    | RedHawk Linux Release 1.1     |

| Previous Release December 2003 | 210    | RedHawk Linux Release 2.0     |

| Current Release May 2005       | 300    | RedHawk Linux Release 2.3     |

| Update September 2005          | 310    | RedHawk Linux Release 2.3-4.1 |

| Update May 2007                | 320    | RedHawk Linux Release 4.2     |

| Update April 2008              | 330    | RedHawk Linux Release 5.1     |

| Update June 2008               | 400    | RedHawk Linux Release 5.1     |

#### Scope of Manual

This manual is intended for users responsible for the installation and use of the Real-Time Clock and Interrupt Module (RCIM) on Concurrent Computer Corporation's iHawk<sup>TM</sup> systems under the RedHawk<sup>TM</sup> Linux<sup>®</sup> operating system.

#### NOTE

Three RCIM models are described in this guide: RCIM I, RCIM II and RCIM III. The use of the term "RCIM" refers to functionality common to all three boards. "RCIM I", "RCIM II" and "RCIM III" refer to the specific boards. Refer to the section "Specifications" on page 1-2 for specifications for each of the boards.

### Structure of Manual

This manual consists of the following:

- Chapter 1, *Introduction*, contains a general overview and specifications for the RCIM boards.

- Chapter 2, *Hardware, Installation and Configuration*, provides a description of the RCIM boards and connectors, as well as installation and configuration instructions.

- Chapter 3, *Functional Description*, provides the general operation, user interfaces and configuration options for the clocks and interrupts available on the RCIM.

- Appendix A, Registers, describes the RCIM registers.

- Appendix B, *Calculating RCIM Cable Propagation Delays*, provides a formula for guarding against propogation delay when chaining RCIMs.

- The *Index* contains an alphabetical reference to key terms and concepts and the pages where they occur in the text.

#### Syntax Notation

The following notation is used throughout this guide:

| italic    | <ul> <li>Books, reference cards, and items that the user must specify appear in <i>italic</i> type. Special terms may also appear in <i>italic</i>.</li> <li>User input appears in list bold type and must be entered exactly as shown. Names of directories, files, commands, options and man page references also appear in list bold type.</li> </ul> |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| list bold |                                                                                                                                                                                                                                                                                                                                                          |  |

| list            | Operating system and program output such as prompts, messages and listings of files and programs appears in list type.                                                                                                                                                                                                                                                              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| []              | Brackets enclose command options and arguments that are optional.<br>You do not type the brackets if you choose to specify these options or<br>arguments.                                                                                                                                                                                                                           |

| hypertext links | When viewing this document online, clicking on chapter, section, figure, table and page number references will display the corresponding text. Clicking on Internet URLs provided in <i>blue</i> type will launch your web browser and display the web site. Clicking on publication names and numbers in <i>red</i> type will display the corresponding manual PDF, if accessible. |

## **Related Publications**

| Title                                                      | Pub No. |

|------------------------------------------------------------|---------|

| RedHawk Linux Release Notes Version x.x                    | 0898003 |

| RedHawk Linux User's Guide                                 | 0898004 |

| RedHawk Linux Frequency-Based Scheduler (FBS) User's Guide | 0898005 |

| iHawk Optimization Guide                                   | 0898011 |

where x.x = release version

# Contents

| Preface                |                                                | iii  |

|------------------------|------------------------------------------------|------|

| Chapter 1 Introduction | on                                             |      |

|                        | Overview                                       | 1-1  |

|                        | Specifications.                                | 1-2  |

| Chapter 2 Hardware,    | Installation and Configuration                 |      |

|                        | Board Descriptions                             | 2-1  |

|                        | RCIM III                                       | 2-2  |

|                        | Board Illustration                             | 2-2  |

|                        | Input and Output Cables and Connectors         | 2-3  |

|                        | Oscillators                                    | 2-3  |

|                        | GPS Antenna                                    | 2-3  |

|                        | External Interrupt I/O Connector               | 2-4  |

|                        | System Identification.                         | 2-5  |

|                        | RCIM II                                        | 2-6  |

|                        | Board Illustration                             | 2-6  |

|                        | Connectors and LEDs                            | 2-6  |

|                        | LED Functions                                  | 2-7  |

|                        | Input and Output Cable Connectors              | 2-8  |

|                        | Oscillators                                    | 2-8  |

|                        | GPS Antenna                                    | 2-8  |

|                        | External Interrupt I/O Connector               | 2-8  |

|                        | System Identification.                         | 2-10 |

|                        | Daisy Chain Cable.                             | 2-10 |

|                        | RCIM I                                         | 2-11 |

|                        | Board Illustration.                            | 2-11 |

|                        | Connectors and LEDs                            | 2-12 |

|                        | LED Functions                                  | 2-12 |

|                        | Output Cable Connector (P2)                    | 2-13 |

|                        | Input Cable Connector (P3).                    | 2-14 |

|                        | External Interrupts Connector (P4)             | 2-14 |

|                        | Debug Visibility Connector (P5).               | 2-15 |

|                        | In-System Programming Interface Connector (P6) | 2-15 |

|                        | System Identification.                         | 2-15 |

|                        | Connection Modes                               | 2-16 |

|                        | Unpacking the RCIM.                            | 2-16 |

|                        | Installation                                   | 2-17 |

|                        | Configuration.                                 | 2-18 |

|                        | Kernel Configuration                           | 2-18 |

|                        | Driver Configuration                           | 2-18 |

|                        | ntp Configuration for GPS Support              | 2-20 |

|                        | Verifying ntp/GPS Operation                    | 2-21 |

|                        | , <u>o</u>                                     | 1    |

## Chapter 3 Functional Description

| Overview                                 | 3-1  |

|------------------------------------------|------|

| Clocks                                   | 3-1  |

| The Tick Clock                           | 3-2  |

| The POSIX Clock                          | 3-2  |

| Direct Access to the Clocks              | 3-3  |

| Synchronizing the Clocks                 | 3-3  |

| The rcim_clocksync Utility               | 3-3  |

| Synchronizing the Tick Clock             | 3-5  |

| Synchronizing the POSIX Clock            | 3-5  |

| Automatic Synchronization                | 3-6  |

| Using GPS for System Timekeeping         | 3-6  |

| Interrupt Processing                     | 3-7  |

| Interrupt Processing Logic               | 3-7  |

| Arming and Enabling DIs and ETIs         | 3-8  |

| Interrupt Recognition Logic              | 3-8  |

| Setting up Distributed Interrupts        | 3-9  |

| Obtaining RCIM Values                    | 3-10 |

| Edge-Triggered Interrupts                | 3-11 |

| ETI Configuration                        | 3-11 |

| ETI Device Files                         | 3-12 |

| User Interface to ETIs                   | 3-12 |

| Distributed ETIs                         | 3-13 |

| Real-Time Clocks (RTCs).                 | 3-13 |

| RTC Device Files                         | 3-13 |

| Distributed RTCs                         | 3-13 |

| User Interface to RTCs                   | 3-14 |

| External Output Interrupts               | 3-14 |

| Configuration                            | 3-15 |

| Programmable Interrupt Generators (PIGs) | 3-15 |

| PIG Device File                          | 3-15 |

| Distributed PIGs                         | 3-16 |

| Distributed Interrupts                   | 3-16 |

| DI Configuration                         | 3-17 |

| DI Device Files                          | 3-18 |

| User Interface to DIs                    | 3-18 |

## Appendix A Registers

| RCIM II Registers   | A-1  |

|---------------------|------|

| RCIM II Address Map | A-1  |

| RCIM II Registers   | A-3  |

| RCIM I Registers    | A-15 |

| RCIM I Address Map  | A-15 |

| RCIM I Registers    | A-16 |

|                     |      |

## Appendix B Calculating RCIM Cable Propagation Delays

| RCIM II | B-1 |

|---------|-----|

| RCIM I  | B-1 |

| ndex Index | x-1 |

|------------|-----|

|------------|-----|

#### Illustrations

| Figure 2-1 RCIM III Board                                                      | 2-2    |

|--------------------------------------------------------------------------------|--------|

| Figure 2-2 RCIM III External Interrupt I/O Connector Pin-outs                  | 2-4    |

| Figure 2-3 RCIM II Board                                                       | 2-6    |

| Figure 2-4 RCIM II Connectors and LED Locations                                | 2-7    |

| Figure 2-5 RCIM II External Interrupt I/O Connector Pin-outs                   | 2-9    |

| Figure 2-6 RCIM I Board                                                        | 2-11   |

| Figure 2-7 RCIM I Connectors and LED Locations                                 | 2-12   |

| Figure 2-8 RCIM I Output Cable Connector (P2) Pin-outs                         | 2-12   |

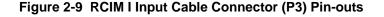

| Figure 2-9 RCIM I Input Cable Connector (P3) Pin-outs                          | 2-13   |

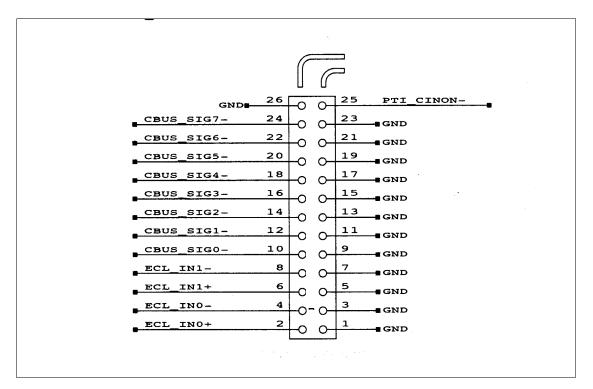

| Figure 2-10 RCIM I External Interrupts Connector (P4) Pin-outs                 | 2-14   |

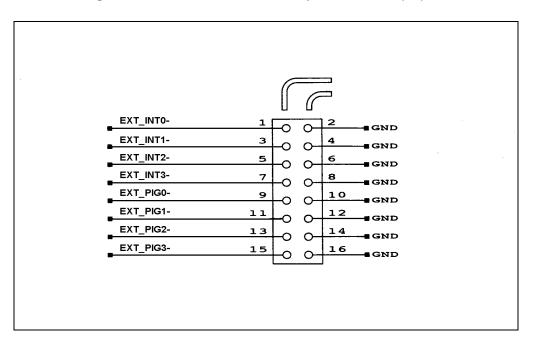

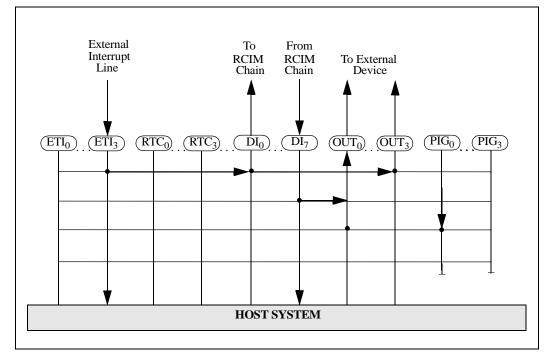

| Figure 3-1 Interrupt Processing Logic                                          | 3-7    |

| Figure 3-2 Distributed Interrupt Operation Example                             | 3-9    |

| • • • •                                                                        |        |

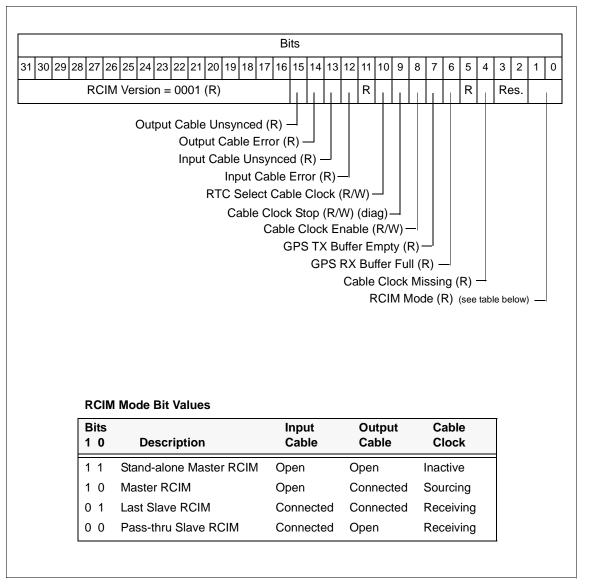

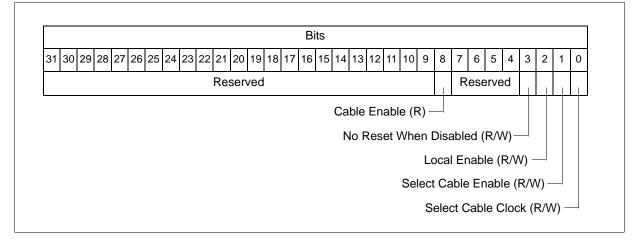

| Figure A-1 RCIM II Board Status/Control Register (BSCR)                        | A-3    |

| Figure A-2 RCIM II Interrupt Enable/Request/Pending/Clear/Arm/Level/Polarity F | -      |

| ters (IER, IRR, IPR, ICR, IAR, ISLR, ISPR)                                     | A-4    |

| Figure A-3 RCIM II External Interrupt Routing Registers (EIRR)                 | A-5    |

| Figure A-4 RCIM II Cable Interrupt Routing Registers (CIRR)                    | A-6    |

| Figure A-5 RCIM II PCI Interrupt Routing Registers (PARR, PBRR, PCRR, PDR      |        |

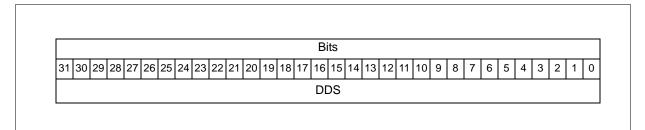

| Figure A-6 RCIM II DDS Adjust Register (DDS)                                   | A-7    |

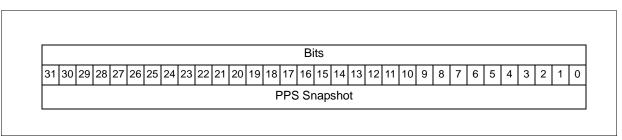

| Figure A-7 RCIM II PPS Snapshot Register (PPS)                                 | A-8    |

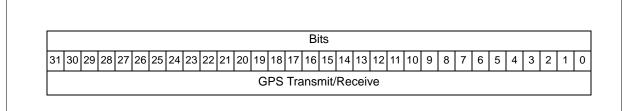

| Figure A-8 RCIM II GPS Transmit/Receive Register (GPS)                         | A-8    |

| Figure A-9 RCIM II Clear Cable Errors Register (CCERR)                         | A-8    |

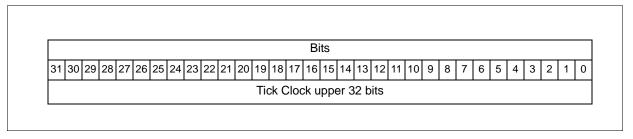

| Figure A-10 RCIM II Tick Clock Upper Register (TCU)                            | A-9    |

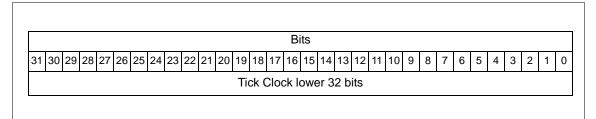

| Figure A-11 RCIM II Tick Clock Lower Register (TCL)                            | A-9    |

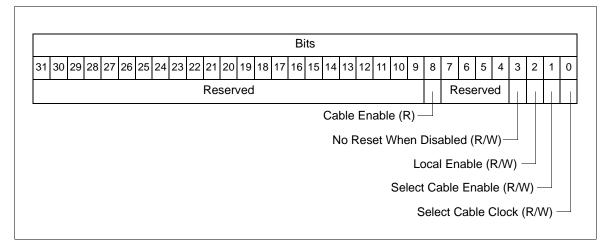

| Figure A-12 RCIM II Tick Clock Status/Control Register (TCSC)                  | A-9    |

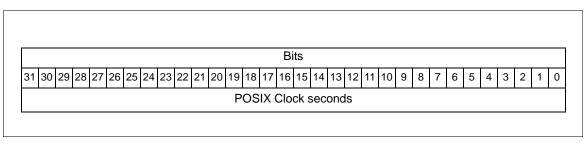

| Figure A-13 RCIM II POSIX Clock Seconds Register (PCS)                         | A-10   |

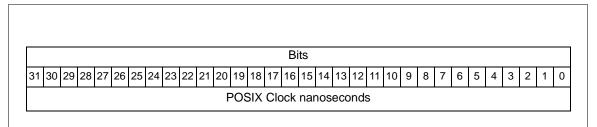

| Figure A-14 RCIM II POSIX Clock Nanoseconds Register (PCN)                     | A-10   |

| Figure A-15 RCIM II POSIX Clock Status/Control Register (PCSC)                 | A-11   |

| Figure A-16 RCIM II POSIX Clock Skip/Add Time Register (PCSAT)                 | A-11   |

| Figure A-17 RCIM II RTC Timer Registers (RTCT)                                 | A-12   |

| Figure A-18 RCIM II RTC Repeat Registers (RTCR)                                | A-12   |

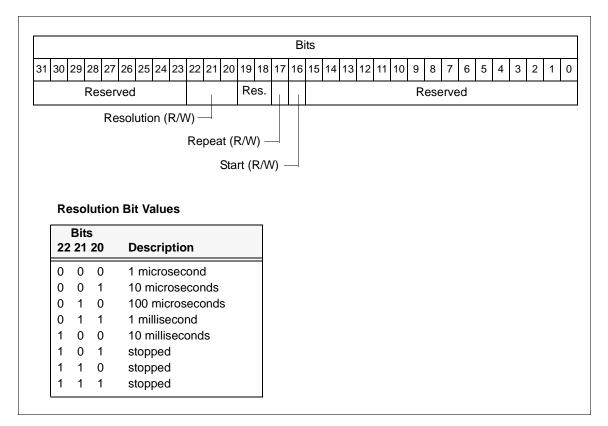

| Figure A-19 RCIM II RTC Control Registers (RTCC)                               | A-13   |

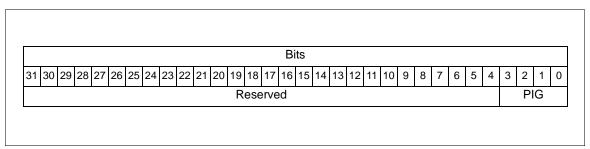

| Figure A-20 RCIM II Programmable Interrupt Generator Register (PIG)            | A-14   |

| Figure A-21 RCIM II Programmable Interrupt Set/Clear Registers (PIGS, PIGC)    | A-14   |

| Figure A-22 RCIM I Board Status/Control Register (BSCR)                        | A-16   |

| Figure A-23 RCIM I Interrupt Enable/Request/Pending/Clear/ARM/Level/Polarity   | Regis- |

| ters (IER, IRR, IPR, ICR, IAR, ISLR, ISPR)                                     | A-17   |

| Figure A-24 RCIM I External Interrupt Routing Register (EIRR)                  | A-18   |

| Figure A-25 RCIM I Cable Interrupt Routing Register (CIRR)                     | A-19   |

| Figure A-26 RCIM I Tick Clock Upper Register (TCU)                             | A-20   |

| Figure A-27 RCIM I Tick Clock Lower Register (TCL)                             | A-20   |

| Figure A-28 RCIM I Tick Clock Status/Control Register (TCSC)                   | A-20   |

| Figure A-29 RCIM I POSIX Clock Seconds Register (PCS)                          | A-21   |

| Figure A-30 RCIM I POSIX Clock Nanoseconds Register (PCN)                      | A-21   |

| Figure A-31 RCIM I POSIX Clock Status/Control Register (PCSC)                  | A-21   |

| Figure A-32 RCIM I RTC Control Registers                                       | A-22   |

| Figure A-33 RCIM I RTC Timer Registers                                         | A-22   |

| Figure A-34 RCIM I Programmable Interrupt Generator Register (PIG)             | A-23   |

| ingue in 5 - Renti i i rogrammable interiupt Generator Register (110)          | 11-23  |

RCIM User's Guide

# 1 Introduction

| Overview       | 1-1 |

|----------------|-----|

| Specifications | 1-2 |

RCIM User's Guide

# 1 Introduction

This chapter provides an overview and specifications for the Real-Time Clock and Interrupt Module (RCIM).

#### NOTE

Three RCIM models are described in this guide: RCIM I, RCIM II and RCIM III. The use of the term "RCIM" refers to functionality common to all three boards. "RCIM I", "RCIM II" and "RCIM III" refer to the specific boards. The section "Specifications" provides specifications for each of the boards.

# **Overview**

The Real-Time Clock and Interrupt Module (RCIM) is a PCI-based card that supports time-critical applications that require rapid response to external events, synchronized clocks and/or synchronized interrupts.

When RCIM boards of various systems are chained together, an interrupt can be simultaneously distributed to all connected RCIMs, and from the RCIMs to all the associated host systems.

A synchronized high-resolution clock is provided so that all the RCIMs in an RCIM chain on multiple systems can share a common time base. It also provides a local POSIX 1003.1 compliant high resolution clock. An optional GPS module allows alignment of the clock to GPS standard time. A high stability oscillator is standard. Optional oscillators improve the accuracy of times measured with the RCIM.

In addition to the clocks, this multi-purpose PCI-based card has the following functionality:

- · connection of external device interrupts

- real time clock timers that can interrupt the system

- programmable interrupt generators which allow generation of an interrupt from an application program

These functions can all generate local interrupts on the system where the RCIM card is installed. When systems are chained together, multiple input and output interrupts can be distributed to other RCIM-connected systems. This allows one timer or one external interrupt or one application program to interrupt multiple RedHawk Linux systems almost simultaneously to create synchronized actions.

# **Specifications**

| Feature                                                    | RCIM III                                                  | RCIM II                                                   | RCIM I                                                    |

|------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|

| Clocks                                                     |                                                           |                                                           |                                                           |

| POSIX                                                      |                                                           |                                                           |                                                           |

| Length                                                     | 64 bits (two 32-bit words)                                | 64 bits (two 32-bit words)                                | 64 bits (two 32-bit words)                                |

| Resolution                                                 | High-order 32 bits–1 second<br>Low-order 32 bits–100 nsec | High-order 32 bits–1 second<br>Low-order 32 bits–400 nsec | High-order 32 bits–1 second<br>Low-order 32 bits–400 nsec |

| Oscillator stability                                       | +/-2.5 PPM                                                | +/-20 PPM                                                 | +/-100 PPM                                                |

| Tick Timer                                                 |                                                           |                                                           |                                                           |

| Length                                                     | 64 bits (two 32-bit words)                                | 64 bits (two 32-bit words)                                | 64 bits (two 32-bit words)                                |

| Resolution                                                 | 64 bit counter of 400 ns ticks                            | 64 bit counter of 400 ns ticks                            | 64 bit counter of 400 ns ticks                            |

| Real-Time Clocks                                           | ·                                                         |                                                           |                                                           |

| Number                                                     | 8                                                         | 8                                                         | 4                                                         |

| Length                                                     | 32 bits                                                   | 32 bits                                                   | 32 bits                                                   |

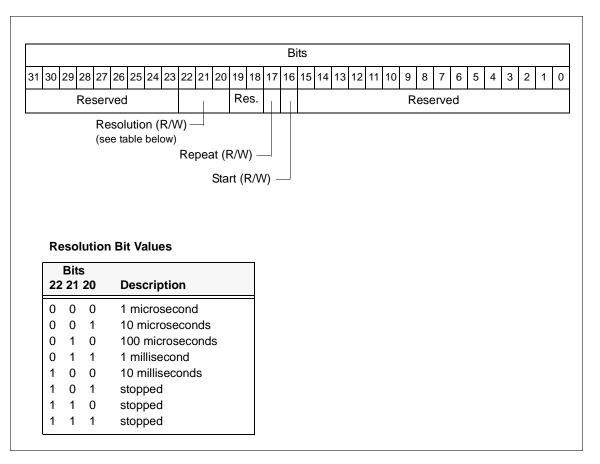

| Resolution                                                 | 1 microsecond<br>(larger values programmable)             | 1 microsecond<br>(larger values programmable)             | 1 microsecond<br>(larger values programmable)             |

| Oscillator stability                                       | +/-2.5 PPM                                                | +/-20 PPM                                                 | +/-100 PPM                                                |

| Local Interrupts                                           |                                                           |                                                           |                                                           |

| External Edge-Triggered Interrupts                         | s 12                                                      | 12                                                        | 4                                                         |

| External Output Interrupts                                 | 12                                                        | 12                                                        | 4                                                         |

| Real-Time Clocks                                           | 8                                                         | 8                                                         | 4                                                         |

| Distributed Interrupts                                     |                                                           | 1                                                         |                                                           |

| Input                                                      | 12                                                        | 12                                                        | 8                                                         |

| Output                                                     | 12                                                        | 12                                                        | 8                                                         |

| Interrupt Response Time                                    |                                                           |                                                           |                                                           |

| Interrupt to user process                                  | < 8 microseconds                                          | < 8 microseconds                                          | < 8 microseconds                                          |

| Packaging                                                  |                                                           | 1                                                         |                                                           |

| Form Factor                                                | PCIe                                                      | PCI                                                       | PCI                                                       |

| Maximum cable length<br>(See Appendix B for calculations.) | TBS                                                       | 32 ft.                                                    | 32 ft.                                                    |

| External Connectors                                        | Molex LFH-60                                              | Molex LFH-60                                              | 16 position .1" Latching Header                           |

| PCI Performance                                            | x1                                                        | 66 MHz 64-bit                                             | 66 MHz 64-bit                                             |

| Options                                                    | GPS Module                                                | GPS Module                                                | None                                                      |

| Environmental                                              |                                                           | 1                                                         |                                                           |

| Operating Temperature                                      | 10° to 40° C                                              | $10^{\circ}$ to $40^{\circ}$ C                            | 10° to 40° C                                              |

| Storage Temperature                                        | -40° to 65° C                                             | -40° to 65° C                                             | -40° to 65° C                                             |

| Relative Humidity                                          | 10 to 90% (non-condensing)                                | 10 to 90% (non-condensing)                                | 10 to 80% (non-condensing)                                |

| Power                                                      |                                                           |                                                           |                                                           |

| Consumption                                                | ~5 watts                                                  | ~5 watts                                                  | ~5 watts                                                  |

# Hardware, Installation and Configuration

| Board Descriptions                             | 2-1  |  |  |  |  |

|------------------------------------------------|------|--|--|--|--|

| RCIM III                                       | 2-2  |  |  |  |  |

| Board Illustration.                            | 2-2  |  |  |  |  |

| Input and Output Cables and Connectors         | 2-3  |  |  |  |  |

| Oscillators                                    | 2-3  |  |  |  |  |

| GPS Antenna                                    | 2-3  |  |  |  |  |

| External Interrupt I/O Connector               | 2-4  |  |  |  |  |

| System Identification.                         | 2-5  |  |  |  |  |

| RCIM II                                        | 2-6  |  |  |  |  |

| Board Illustration.                            | 2-6  |  |  |  |  |

| Connectors and LEDs                            | 2-6  |  |  |  |  |

| LED Functions                                  | 2-7  |  |  |  |  |

| Input and Output Cable Connectors              | 2-8  |  |  |  |  |

| Oscillators                                    | 2-8  |  |  |  |  |

| GPS Antenna.                                   | 2-8  |  |  |  |  |

| External Interrupt I/O Connector               | 2-8  |  |  |  |  |

| System Identification.                         | 2-10 |  |  |  |  |

| Daisy Chain Cable.                             | 2-10 |  |  |  |  |

| RCIM I                                         | 2-11 |  |  |  |  |

| Board Illustration.                            | 2-11 |  |  |  |  |

| Connectors and LEDs                            | 2-12 |  |  |  |  |

| LED Functions                                  | 2-12 |  |  |  |  |

| Output Cable Connector (P2)                    | 2-13 |  |  |  |  |

| Input Cable Connector (P3).                    | 2-14 |  |  |  |  |

| External Interrupts Connector (P4)             | 2-14 |  |  |  |  |

| Debug Visibility Connector (P5)                | 2-15 |  |  |  |  |

| In-System Programming Interface Connector (P6) | 2-15 |  |  |  |  |

| System Identification.                         | 2-15 |  |  |  |  |

| Connection Modes                               | 2-16 |  |  |  |  |

| Unpacking the RCIM.                            | 2-16 |  |  |  |  |

| Installation                                   | 2-17 |  |  |  |  |

| Configuration                                  | 2-18 |  |  |  |  |

| Kernel Configuration                           | 2-18 |  |  |  |  |

| Driver Configuration                           |      |  |  |  |  |

| ntp Configuration for GPS Support              | 2-20 |  |  |  |  |

| Verifying ntp/GPS Operation                    | 2-21 |  |  |  |  |

RCIM User's Guide

# Hardware, Installation and Configuration

This chapter provides a description of the RCIM PCI-based boards as well as installation and configuration information.

# **Board Descriptions**

This section provides illustrations and descriptions of the RCIM III, RCIM II and RCIM I boards.

RCIM II and RCIM I boards mount in a standard PCI slot on a host system. A connector is mounted on each RCIM for connection to external interrupts. A synchronization cable is included for daisy-chaining a master RCIM to one or more slave RCIMs.

The RCIM III board mounts in a standard PCIe slot. A connector is mounted on each RCIM for connection to external interrupts.

#### NOTE

The initial release of the RCIM III board does not support cabling (chaining) boards together or distributing RTC or PIG operations to local Distributed Interrupt devices.

2

# **RCIM III**

# **Board Illustration**

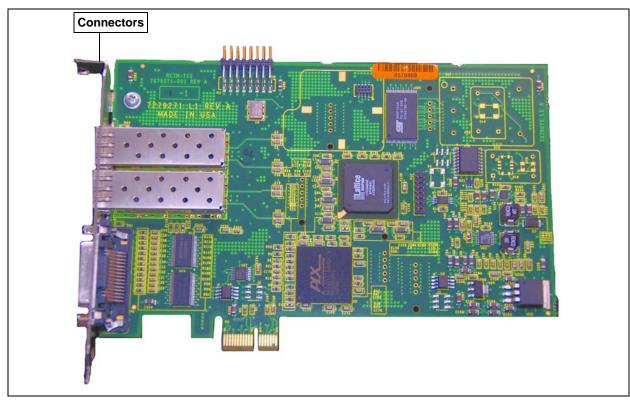

Figure 2-1 shows the RCIM III board.

Figure 2-1 RCIM III Board

### Input and Output Cables and Connectors

The RCIM III uses a pair of standard SFP connectors and cages to interface to the RCIM III cable. The cable is used to communicate interrupts, time stamps and a reference clock between RCIM III boards. The two ports are referenced as "input" and "output". Each port has both a transmit path and a receive path. The RCIM III boards are connected in a loop architecture, with the output port of any RCIM III cabled to the input port of the next RCIM III in the loop. This loop architecture allows two complete paths that communicate in opposite directions around the loop, providing resiliency in situations where a cable is unplugged, an RCIM III board is powered down or the board or cable is faulty.

Active optical SFP transceivers and fiber optic cables are used. The SFP transceivers use LC fiber optic connectors.

#### NOTE

The initial release of the RCIM III board does not support cabling (chaining) boards together or distributing RTC or PIG operations to local Distributed Interrupt devices.

### Oscillators

The temperature compensated crystal oscillator (TCXO) provided with RCIM III is a FOX 924B oscillator, which increases the accuracy of the RCIM III clocks to +/-2.5 parts per million (PPM).

An optional TCXO provides a temperature stability of +/- 210 PPB (parts per billion).

An optional oven controlled crystal oscillator (OCXO) increases the accuracy of the RCIM III clocks from 20 parts per million (PPM) to less than 4 PPM. Temperature stability is +/- 10 PPB (parts per billion).

### **GPS** Antenna

The GPS option on the RCIM III includes an active GPS antenna and coaxial cable.

The antenna receives the GPS satellite signals and passes them to the receiver. The GPS signals are spread spectrum signals in the 1575 MHz range and do not penetrate conductive or opaque surfaces. Therefore, the antenna must be located outdoors with a clear view of the sky.

If a different antenna or cable is used, it should match the following specifications:

- 50 Ohm impedence

- 27 dB gain

- 3.3 volt DC power max 30 ma.

#### **External Interrupt I/O Connector**

The external interrupt I/O connector on the RCIM III is a Molex LFH-60 (Low Force Helix) that provides twelve outputs and twelve inputs.

The external outputs allow equipment to be attached and controlled by the RCIM. The outputs are driven by a multiplexer which can select any of the programmable interrupt generators (PIGs), real-time clock timers (RTCs), edge-triggered interrupts (ETIs) or distributed interrupts (DIs) to drive the output. The selection is controlled by a set of configuration registers.

See Chapter 3 for information on using external output interrupts and programmable interrupts.

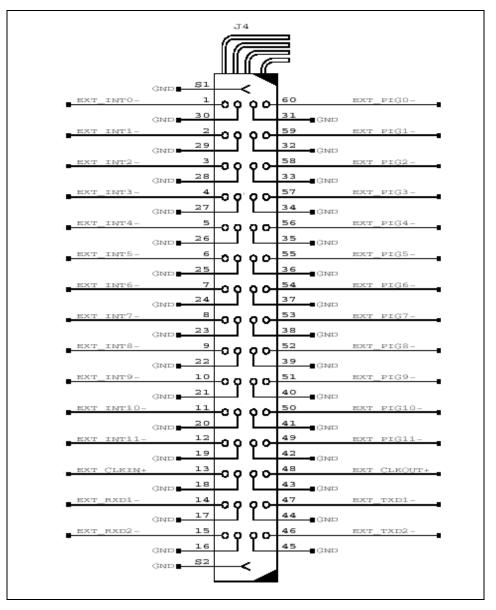

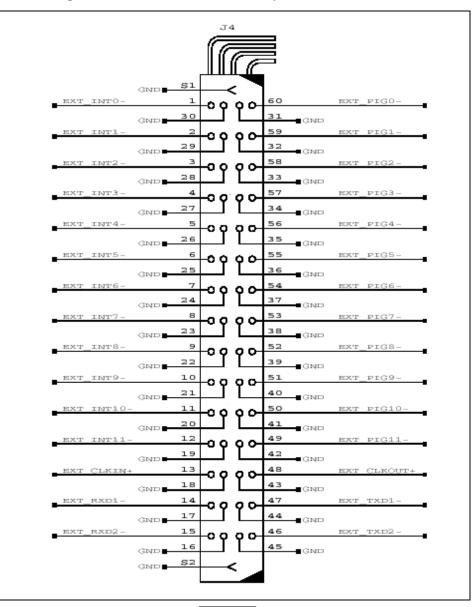

The pin-outs for the external interrupt I/O connector are shown in Figure 2-2.

Figure 2-2 RCIM III External Interrupt I/O Connector Pin-outs

The external interrupt input signals are 5 volt ttl levels. The external interrupt outputs (labeled EXT\_PIG[0-11]) are driven using a 74ABT16240 line driver. The external interrupt inputs are terminated with 180 ohms to +5 volts, 330 ohms and 0.1 uf to ground. To drive this input requires a line driver that can sink at least 30 ma. The input termination limits the speed of the external interrupt signals and helps prevent noise from causing spurious interrupts. Since most line drivers can sink more current than they can source, the falling edge of the signal will be faster.

The signals EXT\_CLKIN and EXT\_CLKOUT are not currently supported.

The signals EXT\_RXD1, EXT\_TXD1, EXT\_RXD2, and EXT\_TXD2 are RS-232 level signals. They are currently used for debug purposes.

#### System Identification

The following output to **lspci(8)** shows the PCI class, vendor and device IDs for the RCIM III (0e:04.0 (*bus:slot.function*) will differ on your system):

# lspci -v | grep -i rcim 0e:04.0 System peripheral: Concurrent Computer Corporation RCIM III Real-Time Clock & Interrupt Module (PCIe) (rev 01) # lspci -ns 0e:04.0 0e:04.0 Class 0880: 1542:9271 (rev 01)

# **RCIM II**

## **Board Illustration**

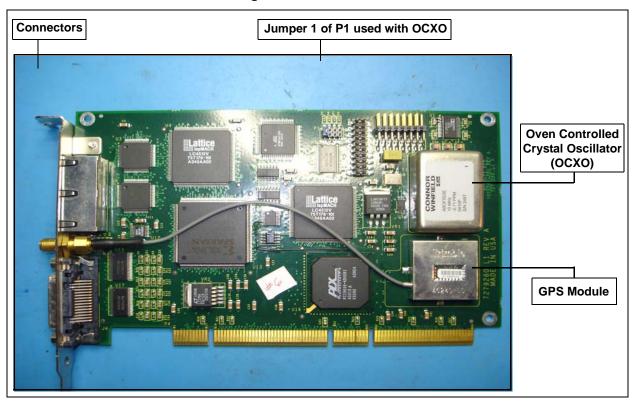

Figure 2-3 shows the RCIM II board with optional high stability OCXO (Oven Controlled Crystal Oscillator) and GPS modules installed.

Figure 2-3 RCIM II Board

## **Connectors and LEDs**

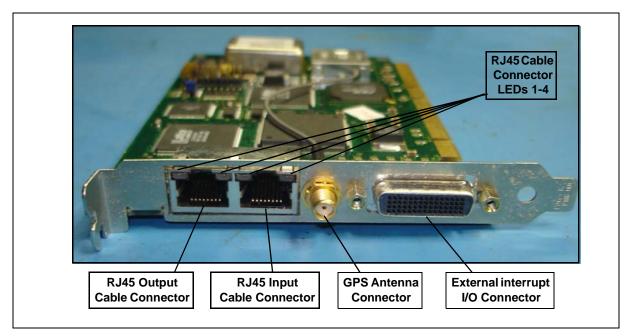

Figure 2-4 shows the input/output connectors and LEDs on the RCIM II board.

Detailed information on the LEDs and each of the connectors is provided in the following sections.

Figure 2-4 RCIM II Connectors and LED Locations

## **LED Functions**

The four LEDs for the RJ45 input and output connectors on the RCIM II board function as follows:

| Connector                     | LED   | Function                                                                                                           |  |  |  |  |  |

|-------------------------------|-------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RJ45 Output                   | LED 1 | Red Failure, Green Activity                                                                                        |  |  |  |  |  |

| Cable Connector               | LED 2 | Cable status:offcable not connectedyellowcable connected but not synchronizedgreencable connected and synchronized |  |  |  |  |  |

| RJ45 Input<br>Cable Connector | LED 3 | Always flashing green                                                                                              |  |  |  |  |  |

|                               | LED 4 | Cable status:offcable not connectedyellowcable connected but not synchronizedgreencable connected and synchronized |  |  |  |  |  |

#### Input and Output Cable Connectors

The output cable connector is used when the RCIM II is either the master, or a slave in the middle of an RCIM chain (see page 2-16 for a description of RCIM modes). The input cable connector is used when the RCIM is acting in slave mode.

The cable attached to the output cable connector is an RJ45 serial synchronization cable (part no. HS002-CBL-10). Refer to the section "Daisy Chain Cable" for more information about the cable.

Note that although RJ45 cables are used with Gigabit Ethernet, the RCIM II cables are not Ethernet compatible.

#### Oscillators

An optional temperature compensated crystal oscillator (TCXO) increases the accuracy of the RCIM II clocks with a temperature stability of +/- 210 PPB (parts per billion).

An optional oven controlled crystal oscillator (OCXO) increases the accuracy of the RCIM II clocks from 20 parts per million (PPM) to less than 4 PPM. Temperature stability is +/- 10 parts per billion.

#### **GPS** Antenna

The GPS option on the RCIM II includes an active GPS antenna and coaxial cable.

The antenna receives the GPS satellite signals and passes them to the receiver. The GPS signals are spread spectrum signals in the 1575 MHz range and do not penetrate conductive or opaque surfaces. Therefore, the antenna must be located outdoors with a clear view of the sky.

If a different antenna or cable is used, it should match the following specifications:

- 50 Ohm impedence

- 27 dB gain

- 3.3 volt DC power max 30 ma.

#### **External Interrupt I/O Connector**

The external interrupt I/O connector on the RCIM II is a Molex LFH-60 (Low Force Helix) that provides twelve outputs and twelve inputs.

The external outputs allow equipment to be attached and controlled by the RCIM. The outputs are driven by a multiplexer which can select any of the programmable interrupt generators (PIGs), real-time clock timers (RTCs), edge-triggered interrupts (ETIs) or distributed interrupts (DIs) to drive the output. The selection is controlled by a set of configuration registers.

See Chapter 3 for information on using external output interrupts and programmable interrupts.

The pin-outs for the external interrupt I/O connector are shown in Figure 2-5.

Figure 2-5 RCIM II External Interrupt I/O Connector Pin-outs

The external interrupt input signals are 5 volt ttl levels. The external interrupt outputs (labeled EXT\_PIG[0-11]) are driven using a 74ABT16240 line driver. The external interrupt inputs are terminated with 180 ohms to +5 volts, 330 ohms and 0.1 uf to ground. To drive this input requires a line driver that can sink at least 30 ma. The input termination limits the speed of the external interrupt signals and helps prevent noise from causing spurious interrupts. Since most line drivers can sink more current than they can source, the falling edge of the signal will be faster.

The signals EXT\_CLKIN and EXT\_CLKOUT are not currently supported.

The signals EXT\_RXD1, EXT\_TXD1, EXT\_RXD2, and EXT\_TXD2 are RS-232 level signals. They are currently used for debug purposes.

#### System Identification

The following output to **lspci(8)** shows the PCI class, vendor and device IDs for the RCIM II (0d:06.0 (*bus:slot.function*) will differ on your system):

# lspci -v | grep -i rcim Od:06.0 System peripheral: Concurrent Computer Corp RCIM II Realtime Clock and Interrupts Module (rev 01) # lspci -ns 0d:06.0 Od:06.0 Class 0880: 1542:9260 (rev 01)

#### **Daisy Chain Cable**

The RCIM II uses an RJ45 serial synchronization cable (part no. HS002-CBL-10) to connect RCIM IIs in an RCIM chain. The serial data on the cable includes parity and framing information which allow cable problems to be detected. Polling is done continuously and messages that report the status of the RCIM II daisy chain cables are output when an error condition is detected. Messages indicating problems will appear on the systems directly connected by a failing link.

The serial cables are point to point connections. The "input" cable refers to the cable going upstream towards the master RCIM. The "output" cable is the downstream connection away from the master.

RCIM: Input cable disconnected. RCIM: Input cable connected. RCIM: Input cable connected but not synchronized. RCIM: Input cable unsynchronized. RCIM: Output cable 0.K. RCIM: Output cable disconnected. RCIM: Output cable connected. RCIM: Output cable connected but not synchronized. RCIM: Output cable unsynchronized. RCIM: Output cable 0.K. RCIM: Cable error on input cable. RCIM: Cable error on output cable.

The "not synchronized" and "unsynchronized" messages indicate that the cable is connected but not answering attempts to communicate. This would be the case if the connected system was powered off.

The last two messages indicate transient errors such as cable parity errors or temporary loss of cable synchronization. If a transient error occurs, it may require a link in the cable to resynchronize. If a distributed interrupt is being broadcast on the cable, it may be lost. Transient errors also affect the synchronization of the tick timers since the cable clock will not reach all of the systems. Refer to Chapter 3 for instructions for synchronizing clocks.

# **RCIM I**

This section provides illustrations and descriptions of the RCIM I board.

## **Board Illustration**

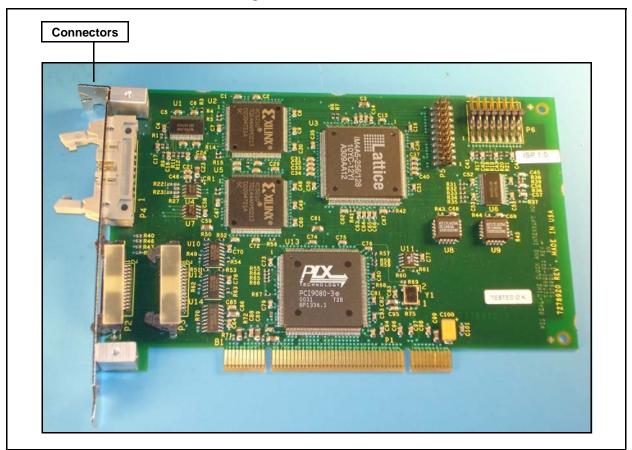

Figure 2-6 shows the RCIM I board.

Figure 2-6 RCIM I Board

## **Connectors and LEDs**

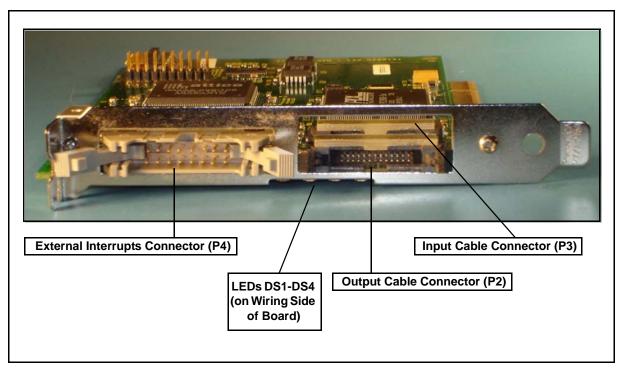

Figure 2-7 shows the input/output connectors and LEDs on the RCIM I board.

Detailed information on the LEDs and each of the connectors is provided in the following sections.

Figure 2-7 RCIM I Connectors and LED Locations

#### **LED Functions**

The four LEDs are on the circuit side of the RCIM I board between the output cable connector (P2) and the external interrupts connector (P4). They function as follows:

| LED    | Number | Function                                                        |

|--------|--------|-----------------------------------------------------------------|

| Red    | DS1    | If on after reset, indicates RCIM module failed power-up reset. |

| Yellow | DS2    | If on, indicates cable clock not connected.                     |

| Green  | DS3    | If on, indicates activity in progress.                          |

| Green  | DS4    | If on, indicates power applied to RCIM.                         |

### **Output Cable Connector (P2)**

The output cable connector is used when the RCIM I is either the master, or a slave in the middle of an RCIM chain (see page 2-16 for a description of RCIM modes). The cable attached to the output cable connector is called a synchronization cable (part no. 6010178-109). The pin-outs for the output cable connector are shown in Figure 2-8.

Figure 2-8 RCIM I Output Cable Connector (P2) Pin-outs

## Input Cable Connector (P3)

The input cable connector is used when the RCIM I is acting in slave mode (see page 2-16 for a description of RCIM modes). The cable attached to the input cable connector is called a synchronization cable (part no. 6010178-109). The pin-outs for the input cable connector are shown in Figure 2-9.

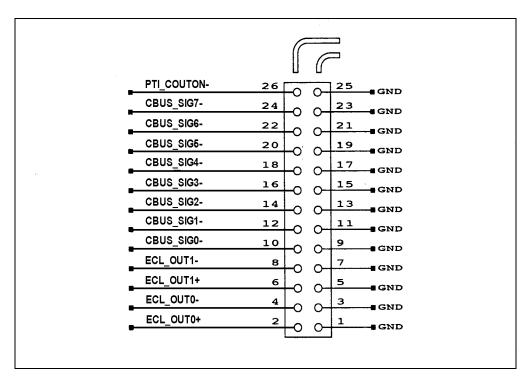

#### **External Interrupts Connector (P4)**

The external interrupts connector on the RCIM I provides four outputs and four inputs.

The external outputs allow equipment to be attached and controlled by the RCIM. The outputs are driven by a multiplexer which can select any of the programmable interrupt generators (PIGs), real-time clock timers (RTCs), edge-triggered interrupts (ETIs) or distributed interrupts (DIs) to drive the output. The selection is controlled by a set of configuration registers.

See Chapter 3 for information on using external output interrupts and programmable interrupts.

Pin-outs for the external interrupts connector are shown in Figure 2-10.

Figure 2-10 RCIM I External Interrupts Connector (P4) Pin-outs

# **Debug Visibility Connector (P5)**

The debug visibility connector is intended for use on the Concurrent Computer Corporation manufacturing floor and should not be used outside of that environment.

#### In-System Programming Interface Connector (P6)

The in-system programming interface connector is intended for use on the Concurrent Computer Corporation manufacturing floor and should not be used outside of that environment.

#### System Identification

The following output to **lspci(8)** shows the PCI class, vendor and device IDs for the RCIM I (0d:06.0 (*bus:slot.function*) will differ on your system):

# lspci -v | grep -i rcim Od:06.0 System peripheral: PLX Technology, Inc. RCIM Realtime Clock and Interrupts Module old ID (rev 01) # lspci -ns 0d:06.0 Od:06.0 Class 0880: 10b5:8845 (rev 01)

# **Connection Modes**

When RCIM boards of various systems are chained together, an interrupt can be simultaneously distributed to all connected RCIMs, and from the RCIMs to all the associated host systems.

#### NOTES

All RCIMs in a chain must be the same model; for example, all RCIM IIs.

The initial release of the RCIM III board does not support cabling (chaining) boards together or distributing RTC or PIG operations to local Distributed Interrupt devices.

If your system will be part of an RCIM chain, it is best to determine the desired connection mode before installing an RCIM; it is easier to connect the cable to the cable connectors before the RCIM is installed.

Note that to reconfigure an RCIM II or RCIM I chain, the systems must be powered off and rebooted after moving the cables. The driver determines if a system is the master RCIM at boot time and configures the master system to control the cable clock and its enable. Swapping the cables without rebooting the systems will result in problems with the cable clock.

An RCIM can be connected in one of the following modes:

| Isolated mode              | There are no connections to any other RCIM.                                                                                                                                                                                   |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master mode                | The RCIM is at the head of a chain of RCIMs. There is no cable connection going into this RCIM, only a cable connection going out. The RCIM master is unique in that it controls the clocks (see Chapter 3 for a discussion). |

| Pass-through<br>Slave mode | The RCIM is connected to two other RCIMs. There is an input<br>cable connection coming from the previous RCIM in the chain, and<br>an output cable connection going to the next RCIM in the chain.                            |

| Final Slave mode           | The RCIM is connected to one other RCIM. There is an input cable connection going into a final slave RCIM but no output cable connection coming out of it.                                                                    |

# **Unpacking the RCIM**

When unpacking the equipment from the shipping container, refer to the packing list and verify that all items are present. Save the packing material for storing and reshipping the equipment.

#### NOTE

If the shipping container is damaged upon receipt, request that the carrier's agent be present during unpacking and inspection of the equipment.

# Installation

Normally, installation and configuration of the card is done by Concurrent Computer Corporation. This information is provided for those cases where an RCIM is added to a system in a post-manufacturing environment.

In order to successfully install the RCIM, you must know if you will be using the RCIM to accept or deliver external interrupts and the mode in which the RCIM will run (isolated, master, pass-through slave or final slave). Refer to the section "Connection Modes" above for details.

#### CAUTION

Avoid touching areas of integrated circuitry as static discharge can damage circuits.

Concurrent Computer Corporation strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components such as disk drives, computer boards, and memory modules can be extremely sensitive to Electrostatic Discharge (ESD). After removing the board from the system or its protective wrapper, place it flat on a grounded, static-free surface, component side up. Do not slide the board over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic strap (available at electronic stores) that is attached to an unpainted metal part of the system chassis.

Use the following procedure to install an RCIM in your system:

- 1. Ensure that your system is powered down.

- 2. Remove the power cable from the system.

- 3. Open the case of your system and identify the PCIe slot (RCIM III) or PCI slot (RCIM II or RCIM I) where you want the RCIM to reside. In general, it is best for the RCIM to be configured in a slot where minimal or no contention with other devices occurs and at the highest IRQ priority possible. Refer to the *iHawk Optimization Guide*, publication number 0898011, for slot configuration guidelines.

#### NOTE: The system must contain only one RCIM board.

- 4. Install the RCIM into the desired slot, securing the card in the slot using the mechanism provided by the case.

- 5. If this is to be part of an RCIM chain, attach the cable as required. See the section "Connection Modes" to determine how to connect the cable based on the connection mode for this system.

- 6. If you are installing an RCIM board equipped with the optional GPS module, attach the GPS antenna lead and mount the antenna. The antenna should be mounted on the rooftop or in an open area. Refer to the sections "Connectors and LEDs" and "GPS Antenna" for more information about the antenna.

- 7. Replace the cover.

- 8. Attach the power cable to the system.

- 9. Apply power and boot the system.

# Configuration

## **Kernel Configuration**

The following RedHawk Linux kernel parameters are associated with the RCIM. All are accessible through the Character Devices selection of the Kernel Configuration GUI and are enabled by default in all the pre-built RedHawk Linux kernels.

| RCIM                                           | This parameter configures the RCIM driver in the kernel. It can be configured as a module, if desired.                                                                                                                                                                                                                            |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCIM_CLOCKSOURCE                               | This parameter enables the RCIM to be used as a source of system time, resulting in more precise system timekeeping.                                                                                                                                                                                                              |

| RCIM_PPS, PPSAPI,<br>PPSAPI_SERIAL,<br>NTP_PPS | These parameters discipline the RCIM tick and POSIX time-of-day<br>registers to the pulse-per-second support of the optional GPS<br>receiver. This provides for time more closely aligned to the official<br>atomic time as defined by the GPS system. These options have no<br>effect if your RCIM does not have GPS capability. |

| RCIM_IRQ_EXTENSION                             | SThis parameter allows other drivers to attach their own interrupt<br>routines to the RCIM driver. The Frequency-based Scheduler<br>(FBS) requires this support.                                                                                                                                                                  |

For complete information about modifying kernel tunables and building a kernel, refer to the *RedHawk Linux User's Guide*, publication number 0898004.

## **Driver Configuration**

When the RCIM driver initializes on a system, it looks at the value of a single tunable (rcim=*RCIMoptions*) for its configuration options. For a statically linked RCIM driver, this tunable can be specified on the GRUB boot loader command line. For an RCIM in module form, this tunable can be specified on the **insmod(8)** command line, or be placed in **modprobe.conf(5)** where the **modprobe(8)** invocation in the startup script /etc/init.d/rcim will find it.

The following functionality is defined with the rcim tunable:

• the manner in which various interrupts will be triggered: rising or falling edge, high or low level

- associations between interrupts, output lines and distributed interrupt lines

- the name of the system in an RCIM chain that has the master RCIM

- whether tick clocks are to run locally or be synchronized with the clock of the master RCIM system in a chain

- whether the RCIM is registered as a clocksource

The rcim tunable accepts a comma-separated list of options. For example:

rcim='host/server1.ccur.com, eti1/rising, di3/high, rtc3|di6'

In this example for an RCIM slave system, the RCIM master system name is server1.ccur.com, edge-triggered interrupt (eti) #1 is configured to trigger on the rising edge, distributed interrupt (di) #3 triggers on a high value, and distributed interrupt line (di) #6 is to be driven by real-time clock timer (rtc) #3.

The sync/nosync options affect clock synchronization across an RCIM chain. "sync" specifies that the RCIM is to use the cable clock driven by the master RCIM's local clock. This is the default. "nosync" specifies that the RCIM uses its local clock.

The clock/noclock options define whether the RCIM is registered as a clocksource for the system. The default is "clock." Note that once the RCIM is registered as a clocksource, it cannot be "unregistered." Also if the RCIM is configured as a module and registered as a clocksource, the module will be locked in ('rmmod rcim" will fail).

On RCIM III and RCIM II systems, the timing sources for RTCs, tick and POSIX clocks can be configured individually, if desired. For example,

```

rcim=nosync/r,sync/tp

```

selects the local clock for the RTCs (r) and the cable clock for the tick (t) and POSIX (p) clocks. If specifiers are not provided for sync and nosync, all three clocks are set according to the option in effect.

Configurations can be modified dynamically using **echo(1)** to write a configuration string, in the format used by the rcim tunable, to **/proc/driver/rcim/config**. For example:

echo eti1/f > /proc/driver/rcim/config

changes eti #1 to trigger on a falling edge. Quotes must be used to surround a configuration request that contains a vertical bar; for example:

echo "rtc0|di1" > /proc/driver/rcim/config

Configuration modifications made in this way are not retained when the system is rebooted. Making these changes requires write permission to the file and should only be made when the RCIM is not in use.

Refer to Chapter 3 or the **rcim(4)** man page for complete information about configuration defaults and selections for each interrupt type.

When configuring the RCIM systems, keep the following in mind:

• When RCIMs are to be chained, all the systems in the RCIM chain must be connected to a network (internet/intranet). The RCIM master functions as

the host. All the slave RCIM systems must include the host's name in its configuration.

- Interrupts, whether operating locally or distributed across an RCIM chain, will be processed according to the values configured on each system. If you wish them to function in a manner different from established defaults, the desired configuration options must be specified.

- When distributing interrupts across the systems in an RCIM chain, all systems must have a compatible configuration for the distributed interrupt lines.

# ntp Configuration for GPS Support

If your system contains the optional GPS module, **ntp** must be installed and configured to use the GPS receiver to synchronize the RCIM's POSIX clock to GPS time. Follow these steps:

1. Verify that the latest ntpd rpm is installed on the system:

```

# rpm -ql ccur-ntp-4.2.2p1-7*

```

\* includes possible updates (.1, .2, etc.) and the architecture type, **i386** or **x86\_64**.

If it is not installed, refer to the *RedHawk Linux Release Notes*, publication number 0898003, for instructions to install this rpm from the RedHawk installation media.

2. The file **/etc/ntp.conf** supplied with the rpm contains the following lines that are required to use the GPS.

server 127.127.8.0 mode 138 prefer #PARSE TSIP (10) + PPS(128)

fudge 127.127.8.0 flag3 1 #enable PPS signal

The following three lines define a pool of world-wide servers that are randomly selected at poweron for time synchronization. This feature acts as the default NTP configuration and serves as backup to GPS. You may wish to include your local country code before "pool" in these entries for best results; e.g., 0.us.pool.ntp.org. See www.pool.ntp.org for more information.

server 0.pool.ntp.org

server 1.pool.ntp.org

server 2.pool.ntp.org

A block of commented out entries beginning with "logfile" is used to configure files used for logging statistics. Uncomment the entries if you wish to enable them.

In addition to the log files, **ntpq(1)** and **ntpdc(1)** are used for NTP monitoring. For more information about NTP, refer to the **ntpd(1)** man page and **www.ntp.org**.

At system poweron, once all data is received from the GPS satellites, accurate timekeeping is available.

## Verifying ntp/GPS Operation

To determine when the GPS is producing accurate time, use the peer listing of **ntpq(1)** as shown below. This example utilizes command line options, however **ntpq** can also be run interactively. Refer to the man page for complete information.

# /usr/sbin/ntpq -np

| remote                      | refid          | st | t | when | poll | reach | delay  | offset | jitter |

|-----------------------------|----------------|----|---|------|------|-------|--------|--------|--------|

|                             |                |    |   |      |      |       |        |        |        |

| <pre>xns2.medbanner.c</pre> | 192.43.244.18  | 2  | u | 33   | 64   | 377   | 72.443 | -2.897 | 11.235 |

| +toshi.keneli.or            | .GPS.          | 1  | u | 43   | 64   | 377   | 27.915 | 0.938  | 2.075  |

| -216.56.81.86               | 193.131.101.50 | 3  | u | 33   | 64   | 377   | 49.388 | -0.579 | 2.710  |

| +new.localdomain            | .GPS.          | 1  | u | 42   | 64   | 377   | 0.182  | 0.010  | 0.020  |

| *GENERIC(0)                 | .GPS.          | 0  | 1 | 46   | 64   | 377   | 0.000  | 0.000  | 0.001  |

The output shows how the system time compares to other time sources. This includes the GPS receiver and other time servers.

The column labeled remote is the hostname of the timeserver. The system new.localdomain is a local network time server; GENERIC(0) is the GPS attached to the RCIM. The other lines are time servers assigned by pool.ntp.org. The first column indicates which servers are being selected for synchronization. The '\*' in front of GENERIC(0) indicates that the RCIM GPS receiver is being used as the system peer.

The columns delay, offset, and jitter are all times in milliseconds. The offset is the difference between the local system time and the time source. In this case we are synchronized to the GPS receiver to microsecond accuracy.

The delay field is the measured network delay to exchange the time with the remote server.

The jitter measures the difference between offset values from the same source.

The refid indicates where the remote system gets its time.

The st column is the stratum number. A stratum zero system should have a direct connection to an authoritative source.

The poll column shows how frequently this server is being polled. The when column is the time in seconds since the last poll.

The reach column is a bitmap in octal which shows if recent polls have been successful. The value 377 would indicate that the last 8 polls succeeded.

Another indicator is through the **ntpq clockvar** command:

```

# /usr/sbin/ntpq

ntpq> clockvar

assID=0 status=0003 clk_okay, last_clk_fault,

device="Trimble GPS (TSIP) receiver", timecode="\x10\xff\x02\x10",

poll=52, noreply=0, badformat=0, baddata=0, fudgetime1=20.000,

stratum=0, refid=GPS, flags=4,

refclock_ppstime="c66be732.00000000 Tue, Jun 28 2005 15:11:46.000",

refclock time="c66be734.03ffffff Tue, Jun 28 2005 15:11:48.015",

```

```

refclock_status="TIME CODE; PPS; POSITION; (LEAP INDICATION; PPS SIGNAL; POSITION)",

refclock_format="Trimble TSIP",

refclock_states="*NOMINAL: 00:54:26 (98.04%); NO RESPONSE: 00:00:02 (0.06%); FAULT:

00:01:03 (1.89%); running time: 00:55:31",

trimble tracking status[08]="ch=4, acq=ACQ, eph=19, signal level= 6.40, elevation= 9.12,

azimuth= 34.35, collecting data",

trimble satview="mode: 2D-AUTO, PDOP 8.96, HDOP 8.91, VDOP 1.00, TDOP 2.90, 3 satellites

in view: 18, 26, 29",

trimble tracking status[10]="ch=0, acq=ACQ, eph=3, signal level= 2.60, elevation= 18.18,

azimuth= 86.56, collecting data",

trimble_tracking_status[18]="ch=1, acq=ACQ, eph=19, signal_level= 5.20, elevation= 39.47,

azimuth= 289.19, collecting data",

trimble_tracking_status[26]="ch=2, acq=ACQ, eph=19, signal_level= 15.40, elevation= 69.34,

azimuth= 49.55, collecting data",

trimble tracking status [29] = "ch=3, acq=ACQ, eph=19, signal level= 15.80, elevation= 52.49,

azimuth= 48.45, collecting data",

trimble receiver health="doing position fixes, Battery backup failed",

trimble status="machine id 0x5a, Battery Powered Time Clock Fault, Superpackets

supported",

gps position ext(XYZ)="x= 1445085.4m, y= -4476862.4m, z= 4277122.9m",

gps_position_ext(LLA)="lat 42.379423 N, lon 71.531318 W, alt 88.35m",

trimble tracking status[15]="ch=7, acq=ACQ, eph=3, signal level= 3.00, elevation= 28.28,

azimuth= 311.83, collecting data",

trimble_tracking_status[09]="ch=4, acq=ACQ, eph=3, signal_level= 1.60, elevation= 23.21,

azimuth= 163.20, collecting data"

ntpq>

```

The refclock\_states message in this example indicates that 98.04% of the time the GPS is receiving useful data. A higher nominal number indicates the most accuracy.

Additional information is provided by many other messages in this output. Refer to **ntpq(1)** for complete details

# 3 Functional Description

| Overview                                 | 3-1  |

|------------------------------------------|------|

| Clocks                                   | 3-1  |

| The Tick Clock                           | 3-2  |

| The POSIX Clock                          | 3-2  |

| Direct Access to the Clocks              | 3-3  |

| Synchronizing the Clocks                 | 3-3  |

| The rcim_clocksync Utility               | 3-3  |

| Synchronizing the Tick Clock             | 3-5  |

| Synchronizing the POSIX Clock.           | 3-5  |

| Automatic Synchronization.               | 3-6  |

| Using GPS for System Timekeeping         | 3-6  |

| Interrupt Processing                     | 3-7  |

| Interrupt Processing Logic               | 3-7  |

| Arming and Enabling DIs and ETIs         | 3-8  |

| Interrupt Recognition Logic              | 3-8  |

| Setting up Distributed Interrupts        | 3-9  |

| Obtaining RCIM Values                    | 3-10 |

| Edge-Triggered Interrupts                | 3-11 |

| ETI Configuration                        | 3-11 |

| ETI Device Files                         | 3-12 |

| User Interface to ETIs                   | 3-12 |

| Distributed ETIs                         | 3-13 |

| Real-Time Clocks (RTCs)                  | 3-13 |

| RTC Device Files                         | 3-13 |

| Distributed RTCs                         | 3-13 |

| User Interface to RTCs                   | 3-14 |

| External Output Interrupts               | 3-14 |

| Configuration                            | 3-15 |

| Programmable Interrupt Generators (PIGs) | 3-15 |

| PIG Device File                          | 3-15 |

| Distributed PIGs                         | 3-16 |

| Distributed Interrupts                   | 3-16 |

| DI Configuration                         | 3-17 |

| DI Device Files                          | 3-18 |

| User Interface to DIs                    | 3-18 |

RCIM User's Guide

This chapter describes the clocks and interrupt capabilities provided by the RCIM and the user interfaces for each.

#### NOTE

The initial release of the RCIM III board does not support cabling (chaining) boards together or distributing RTC or PIG operations to local Distributed Interrupt devices.

## Overview

The Real-Time Clock and Interrupt Module (RCIM) provides two non-interrupting clocks. One of these clocks can be synchronized with all the RCIMs in an RCIM chain to provide a common time stamp across systems. The other clock is POSIX 1003.1 compliant and, although not synchronized across the RCIM chain, it increments in unison with the other clock on the RCIM board and can be set to a specific time.

In addition to the clocks, the following methods for handling signal processing (interrupts) are available:

- Edge-Triggered Interrupts (ETIs)

- Real-Time Clocks (RTCs)

- External Output Interrupts

- Programmable Interrupt Generators (PIGs)

- Distributed Interrupts (DIs)

These interrupts operate locally on an RCIM system or can be distributed across all RCIM systems in an RCIM chain. The **open(2)**, **close(2)** and **ioctl(2)** system calls are used to manipulate the interrupts. Separate device files are associated with each interrupt.

The clocks and interrupts are described in this chapter.

## Clocks

The RCIM provides two non-interrupting clocks, which are fully explained in the sections that follow.

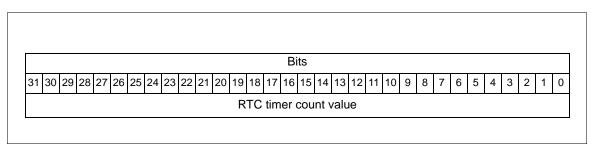

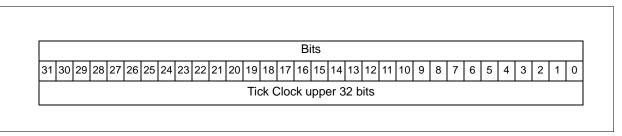

tick a 64-bit non-interrupting clock that increments by one on each tick of the common 400ns clock signal. This clock can be reset to zero and synchronized across the RCIM chain, providing a common time stamp.

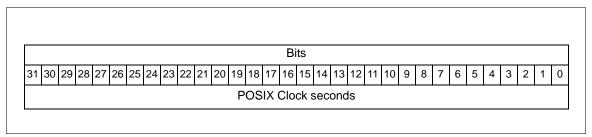

POSIX a 64-bit non-interrupting counter encoded in POSIX 1003.1 format. The upper 32 bits contain seconds and the lower 32 bits

contain nanoseconds. This clock is incremented on each tick of the common clock signal. It is primarily used as a high-resolution local clock. It can be configured to synchronize system time with GPS standard time on boards equipped with GPS.

All clocks on all RCIMs in the chain are incremented in unison, as they are all driven by a common clock signal emanating from the master RCIM.

When an RCIM board is part of an RCIM chain, the tick clocks on all slave RCIMs are incremented and cleared according to the synchronization being done to the tick clock on the master RCIM. The POSIX clocks can each have a value written to it; however, changing the POSIX clock of one RCIM board does not change the value of the POSIX clocks of any of the other RCIM boards in the chain.

## The Tick Clock

The tick clock is a 64-bit non-interrupting counter that increments by one on each tick of the common clock signal. Although it cannot be set to a specific time, it can be incremented or set to zero. Hence the tick clock cannot be adjusted on the fly to approximate the current time of day as would be required of a true time-of-day clock. On RCIM I systems, the system clock is synchronized with the tick clock.

When an RCIM board is part of an RCIM chain, the tick clocks on all slave RCIMs are incremented and cleared in synchronization with whatever incrementing and clearing is done to the tick clock located on the master RCIM.

The tick clock can be read on any system, master or slave, using direct reads when the device file /dev/rcim/sclk is mapped into the address space of a program. See the section "Direct Access to the Clocks" below for details.

By default, tick clock initialization (zeroing) and synchronization with other tick clocks on the RCIM chain occur automatically whenever the RCIM master boots. Initializing and synchronizing tick clocks is accomplished using the **rcim\_clocksync(1)** command. See the sections "Synchronizing the Tick Clock" and "The rcim\_clocksync Utility" below for details.

### The POSIX Clock

The POSIX clock is a 64-bit non-interrupting counter encoded in POSIX 1003.1 format. The upper 32 bits contain seconds and the lower 32 bits contain nanoseconds. This clock is incremented on each tick of the common clock signal. On RCIM III and RCIM II systems, the system clock is synchronized with the POSIX clock.

The POSIX clock is accessed in a manner similar to the tick clock in that the same utilities and device files are used. The POSIX clock can be loaded with any desired time; however, the value loaded is not synchronized with other clocks in an RCIM chain. Only the POSIX clock of the RCIM attached to the host is updated. See the section "Direct Access to the Clocks" below for details about accessing the POSIX clock. Although the RCIM board has no hardware support for setting the POSIX clocks of all boards to a consistent value, it is possible to pause the operation of the RCIM board chain, synchronize the POSIX clock values during the pause using the **rcim\_clocksync(1)** command on each of the systems, then restart the RCIM board chain. See the section "Synchronizing the POSIX Clock" later in this chapter for instructions.

On an RCIM system with GPS module and NTP running, the GPS receiver is used to synchronize the POSIX clock on the RCIM on which it is attached to GPS time. See the section "Using GPS for System Timekeeping" for details.

## **Direct Access to the Clocks**

The device file /dev/rcim/sclk can be used to access the RCIM clocks directly using mmap(2). From the address returned by mmap, the following offsets are used to access the clock fields:

| 0x0   | upper 32-bits of tick clock             |

|-------|-----------------------------------------|

| 0x8   | lower 32-bits of tick clock             |

| 0x10  | status and control (cannot be modified) |

| 0x100 | POSIX clock seconds                     |

| 0x108 | POSIX clock nanoseconds                 |

| 0x110 | status and control (cannot be modified) |

These offsets are defined in the header file /usr/include/linux/rcim.h (with names beginning with RCIM\_SYNCCLOCK\_).

To set the value of the POSIX clock, the **rcim\_clocksync(1)** utility can be used in interactive mode using the "update" command.

## Synchronizing the Clocks

The sections below describe the techniques and tools used to synchronize the clocks on the RCIM.

#### The rcim\_clocksync Utility

The **rcim\_clocksync(1)** utility can be used to reset the tick clocks on all connected RCIMs to zero to provide a common time stamp across the system. This synchronization operation occurs automatically when the RCIM master system boots. As slave systems become available, it will be necessary to reissue this command to synchronize the tick clocks across the RCIM chain, however, this can be automated (see the section "Automatic Synchronization" below). **rcim\_clocksync** can also be used to synchronize the POSIX clocks on all connected RCIMs. This procedure is described in the section "Synchronizing the POSIX Clock."

Note that the system clock is synchronized with the RCIM and when **rcim\_clocksync** is run other than at system boot, there are consequences and should be used with caution. On RCIM III and RCIM II, master and slave system times are synchronized with the POSIX clock; on RCIM I, the times are synchronized with the tick clock. When system time stops advancing, time-based functions using those clocks will stop.

Synchronization always succeeds on the RCIM master or isolated system; an error is returned if synchronization is attempted on an RCIM slave system.

Specifying **rcim\_clocksync** with no options on the RCIM master system synchronizes all tick clocks in the RCIM chain.

rcim\_clocksync takes the following options:

- -i interactive mode (see below)

- -m prints the configured hostname where the RCIM master is located (see "Configuration" in Chapter 2).

- -s prints the RCIM connection state

When interactive mode is invoked, a display similar to the following example provides configuration and status information updated every two seconds, as well as command usage. These items are explained below.

RCIM is isolated RCIM version: 1 Configured RCIM master hostname is Not Configured Clock status and values ... cable signal : ENABLED tick timer : CABLE\_ENABLE LOCAL\_ENABLE posix clock : CABLE\_ENABLE LOCAL\_ENABLE tick timer : 10.3361 seconds ( 25840213 ticks) posix clock : 18665.4696 seconds operations are: - synchronize clocks S 0[tp] - stop clock ([t]ick/[p]osix) 1[tp] - start clock ([t]ick/[p]osix) w[tp] - update clock value ([t]ick/[p]osix) i[tp] - isolate clock ([t]ick/[p]osix) c[tp] - connect clock ([t]ick/[p]osix) d - disable cable clock signal - enable cable clock signal е - quit q enter operation:

- RCIM is indicates the RCIM mode for this system: master, pass-through slave, final slave or isolated

- RCIM version is the RCIM version number

- Configured RCIM master hostname is

indicates the hostname of the RCIM master. This must be configured using the host configuration option (see "Configuration" in Chapter 2)

cable signal is one of the following:

ENABLED/DISABLED – For the RCIM master, indicates if the cable clock signal is being propagated to slaves. For RCIM slaves, indicates if clocks are being driven by the RCIM master or if ticking locally (without synchronization).

CLOCK\_MISSING – Error condition indicating cable clock signal is not being properly propagated to slaves.

CLOCK STOPPED – Error condition indicating cable clock signal has been stopped.

| Status:<br>tick timer<br>posix clock | is one of the following:                                                                                                                                                                                                                                                                                         |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|