Adding a new board to your iHawk system? Looking to improve overall system performance?

Need to understand more about the PCI subsystem and how it affects system performance?

Go to Chapter 2 for a quick reference

to recommended board placements on individual iHawk systems.

Go to Chapter 3 for an in-depth discussion of the factors that affect performance and tools you can use.

0898011-110 April 2008 Copyright 2008 by Concurrent Computer Corporation. All rights reserved. This publication or any part thereof is intended for use with Concurrent products by Concurrent personnel, customers, and end–users. It may not be reproduced in any form without the written permission of the publisher.

The information contained in this document is believed to be correct at the time of publication. It is subject to change without notice. Concurrent makes no warranties, expressed or implied, concerning the information contained in this document.

To report an error or comment on a specific portion of the manual, photocopy the page in question and mark the correction or comment on the copy. Mail the copy (and any additional comments) to Concurrent Computer Corporation, 2881 Gateway Drive, Pompano Beach, Florida, 33069. Mark the envelope "Attention: Publications **Department**." This publication may not be reproduced for any other reason in any form without written permission of the publisher.

Concurrent Computer Corporation and its logo are registered trademarks of Concurrent Computer Corporation. All other Concurrent product names are trademarks of Concurrent while all other product names are trademarks or registered trademarks of their respective owners. Linux® is used pursuant to a sublicense from the Linux Mark Institute.

Printed in U.S.A.

| Revision History | Date       | Level |

|------------------|------------|-------|

| Original Release | May 2005   | 000   |

| Minor Update     | July 2006  | 010   |

| Restructure      | May 2007   | 100   |

| Update           | April 2008 | 110   |

#### **Scope of Manual**

This manual is directed toward those responsible for installation, configuration and administration of Concurrent iHawk computer systems.

Even though this guide represents a limited subset of architectures offered by Concurrent Computer Corporation, these guidelines may be helpful in improving performance on other PCI-based systems running one of Concurrent's real-time Linux operating systems.

#### **Structure of Manual**

This guide consists of the following sections:

- Chapter 1, Overview, explains the purpose of this guide and how to use it.

- Chapter 2, *Configuration Recommendations*, provides PCI slot and bus layouts and recommendations for configuring PCI boards based on the IRQ management scheme used on each of the iHawk systems.

- Chapter 3, *Performance Factors in Configuring iHawks*, provides in-depth discussions of how PCI board configuration and IRQ management can be manipulated to improve system performance.

- The *Glossary* provides definitions of terms used throughout this guide.

- The *Index* contains an alphabetical reference to key terms and concepts and the pages where they occur in the text.

#### **Related Publications**

| Concurrent Documentation                                    | Pub No. |  |  |

|-------------------------------------------------------------|---------|--|--|

| RedHawk Linux Operating System                              |         |  |  |

| RedHawk Linux Release Notes                                 | 0898003 |  |  |

| RedHawk Linux User's Guide                                  | 0898004 |  |  |

| SUSE Linux Enterprise Real Time Operating System            |         |  |  |

| SUSE Linux Enterprise Real Time 10 Release Notes            | 0898206 |  |  |

| SUSE Linux Enterprise Real Time User's Guide                | 0898204 |  |  |

| RCIM PCI Form Factor                                        |         |  |  |

| Real-Time Clock and Interrupt Module (RCIM)<br>User's Guide | 0898007 |  |  |

Preface

# Contents

#### Chapter 1 Overview

| How to Use This Guide                                | 1-1 |

|------------------------------------------------------|-----|

| General Factors in IRQ Processing and Bus Contention | 1-2 |

#### Chapter 2 Configuration Recommendations

| How to Use the IRQ Priority Management Tables         | 2-1  |

|-------------------------------------------------------|------|

| Quick Reference                                       | 2-1  |

| Slot Priority vs. Device Priority vs. System Priority | 2-1  |

| Installing Add-on Cards                               | 2-3  |

| iHawk Configurations                                  | 2-3  |

| iHawk Model HR430.                                    | 2-4  |

| Specifications                                        | 2-4  |

| PCI Bus and Slot Layout                               | 2-4  |

| IRQ Priority Management                               | 2-5  |

| iHawk Model HR210.                                    | 2-6  |

| Specifications                                        | 2-6  |

| PCI Bus and Slot Layout                               | 2-6  |

| IRQ Priority Management                               | 2-7  |

| iHawk Model HQ685                                     | 2-8  |

| Specifications                                        | 2-8  |

| PCI Bus and Slot Layout                               | 2-8  |

| IRQ Priority Management                               | 2-9  |

| iHawk Model HQ680                                     | 2-10 |

| Specifications                                        | 2-10 |

| PCI Bus and Slot Layout                               | 2-10 |

| IRQ Priority Management                               | 2-11 |

| iHawk Model HQ665                                     | 2-12 |

| Specifications                                        | 2-12 |

| PCI Bus and Slot Layout                               | 2-12 |

| IRQ Priority Management                               | 2-13 |

| iHawk Model HQ660                                     | 2-14 |

| Specifications                                        | 2-14 |

| PCI Bus and Slot Layout                               | 2-14 |

| IRQ Priority Management                               | 2-15 |

| iHawk Model HQ460                                     | 2-16 |

| Specifications                                        | 2-16 |

| PCI Bus and Slot Layout                               | 2-16 |

| IRQ Priority Management                               | 2-17 |

| iHawk Model HQ285                                     | 2-18 |

| Specifications                                        | 2-18 |

| PCI Bus and Slot Layout                               | 2-18 |

| IRQ Priority Management                               | 2-19 |

| iHawk Model HQ280                                     | 2-20 |

| Specifications                                        | 2-20 |

| PCI Bus and Slot Layout                               | 2-20 |

| IRQ Priority Management                               | 2-21 |

| iHawk Model HQ265       | 2-22 |

|-------------------------|------|

| Specifications          | 2-22 |

| PCI Bus and Slot Layout | 2-22 |

| IRQ Priority Management | 2-23 |

| iHawk Model HQ067       | 2-24 |

| Specifications          | 2-24 |

| PCI Bus and Slot Layout | 2-24 |

| IRQ Priority Management | 2-25 |

| iHawk Model HQ047       | 2-26 |

| Specifications          | 2-26 |

| PCI Bus and Slot Layout | 2-26 |

| IRQ Priority Management | 2-27 |

#### Chapter 3 Performance Factors in Configuring iHawks

| iHawk Overview                                         | 3-1    |

|--------------------------------------------------------|--------|

| How to Configure iHawks for Performance                | 3-1    |

| PCI, PCIe and PCI-X                                    | 3-3    |

| PCI Bus Architecture                                   | 3-4    |

| Shared Data Paths on PCI and PCI-X Parallel Buses.     | 3-4    |

| Unique Data Paths on PCIe                              | 3-5    |

| Bandwidth                                              | 3-5    |

| Determinism                                            | 3-6    |

| Latency                                                | 3-6    |

| PCI Expansion                                          | 3-7    |

| Understanding IRQ Management                           | 3-7    |

| IRQ Basics                                             | 3-7    |

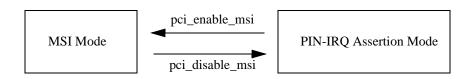

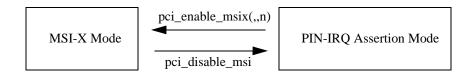

| Message Signaled Interrupts (MSI/MSI-X)                | 3-8    |

| Shared/Nonshared IRQs                                  | 3-8    |

| System Requirements for MSI/MSI-X Support              | 3-9    |

| PCI Capability List and MSI/MSI-X Capability Structure | 3-9    |

| MSI/MSI-X Mode vs. Legacy Mode                         | 3-10   |

| How IRQs are Assigned                                  | 3-11   |

| ACPI                                                   | 3-12   |

| IRQ Priorities.                                        | 3-13   |

| Shared Vectors and lsirq(8)                            | 3-14   |

| Managing IRQ Assignments                               | 3-16   |

| BIOS Setting Recommendations                           | 3-17   |

|                                                        |        |

| Glossary                                               | sary-1 |

| Index                                                  | ndex-1 |

# 1 Overview

| How to Use This Guide                                | 1-1 |

|------------------------------------------------------|-----|

| General Factors in IRQ Processing and Bus Contention | 1-2 |

iHawk Optimization Guide

## How to Use This Guide

Whether you are initially configuring an iHawk system, installing an add-on board or tuning system performance, use the recommendations in this guide to help determine the most desirable and optimal configuration possible for your system.

How PCI slots are populated, the types and characteristics of PCI buses on a system and IRQ priority management schemes all affect system performance. In general you should consider two things:

- IRQ processing

- Bus contention

This guide serves to document these issues and attempts to suggest methods you can use to find a configuration that does not negatively impact your particular application.

As you read through this guide, understand that you will not find the perfect configuration for your system neatly contained in a single table. **The tables in Chapter 2 of this guide are provided as an EXAMPLE ONLY in order to illustrate concepts.** Variations in kernel releases and BIOS revisions make it impossible to provide a single reference for every system.

Go to Chapter 3 to understand the impact of IRQ processing and bus contention within the context of your application. Tools provided in Concurrent's real-time Linux operating systems for troubleshooting your system's PCI assignments and values are also described. For details beyond the scope of this manual, refer to the manufacturer's system guides.

#### NOTE

You may find differences between spec sheets, diagrams printed on the case of your system and the contents of this guide. Use the lsirq(8) and lspci(8) tools together with this guide to find the correct bus layout and IRQ assignments for your system.

# **General Factors in IRQ Processing and Bus Contention**

Here are some basic facts to keep in mind as you use this guide.

Factors that relate to IRQ processing include:

- IRQs are prioritized at the hardware level.

- Hardware interrupts preempt software interrupts.

- All interrupts preempt all software processes.

- PCI IRQs can be shared.

- IRQs are assigned by the kernel based on hardware resources and device discovery.

- IRQ assignment is complex and somewhat unpredictable.

- Reconfiguring hardware may or may not affect IRQ assignments.

- The trend is that slower buses get lower priority IRQs.

Factors that relate to PCI bus contention include:

- Devices on the same PCI bus can only run at the speed of the slowest device.

- Only one device at a time can access the PCI bus.

- PCI latency describes the number of bus cycles a device is allocated per request.

- Different devices have different PCI bus latencies.

- High bandwidth devices have higher PCI bus latencies.

- PCI buses connect to the system bus through a bridge chip.

- There can be multiple independent PCI buses in a system.

- Devices are assigned a logical slot address.

- More than one logical slot address can be assigned to a phyiscal slot.

Chapter 3 discusses these factors in greater length.

Here are some example scenarios for configuring Concurrent's iHawk systems with the Real-time Clock and Interrupt Module (RCIM), or any other real-time device:

The ideal configuration:

- The RCIM has the top priority IRQ.

- The IRQ is unshared.

- The RCIM is on its own bus.

The worst configuration:

- The RCIM has the lowest priority IRQ.

- The IRQ is shared with several busy devices.

- The RCIM shares the bus with several busy devices with high PCI latencies.

In reality, you may be forced to choose a compromise:

- The RCIM does not have the top priority IRQ.

- The IRQ is shared with inactive devices.

- The RCIM shares the bus with devices that don't hog the bus.

# **Configuration Recommendations**

| How to Use the IRQ Priority Management Tables         | 1-1  |

|-------------------------------------------------------|------|

| Quick Reference                                       | 1-1  |

| Slot Priority vs. Device Priority vs. System Priority | 1-1  |

| Installing Add-on Cards                               | 1-3  |

| iHawk Configurations                                  | 1-3  |

| iHawk Model HR430                                     | 1-4  |

| Specifications                                        | 1-4  |

| PCI Bus and Slot Layout                               | 1-4  |

| IRQ Priority Management                               | 1-5  |

| iHawk Model HR210                                     | 1-6  |

| Specifications                                        | 1-6  |

| PCI Bus and Slot Layout                               | 1-6  |

| IRQ Priority Management                               | 1-7  |

| iHawk Model HQ685                                     | 1-8  |

| Specifications                                        | 1-8  |

| PCI Bus and Slot Layout                               | 1-8  |

| IRQ Priority Management                               | 1-9  |

| iHawk Model HQ680                                     | 1-10 |

| Specifications                                        | 1-10 |

| PCI Bus and Slot Layout                               | 1-10 |

| IRQ Priority Management                               | 1-11 |

| iHawk Model HQ665                                     | 1-12 |

| Specifications                                        | 1-12 |

| PCI Bus and Slot Layout                               | 1-12 |

| IRQ Priority Management                               | 1-13 |

| iHawk Model HQ660                                     | 1-14 |

| Specifications                                        | 1-14 |

| PCI Bus and Slot Layout                               | 1-14 |

| IRQ Priority Management                               | 1-15 |

| iHawk Model HQ460                                     | 1-16 |

| Specifications                                        | 1-16 |

|                                                       | 1-16 |

| IRQ Priority Management                               | 1-17 |

| ι                                                     | 1-18 |

| Specifications                                        | 1-18 |

|                                                       | 1-18 |

| IRQ Priority Management                               | 1-19 |

| iHawk Model HQ280                                     | 1-20 |

| Specifications                                        | 1-20 |

| PCI Bus and Slot Layout                               | 1-20 |

| IRQ Priority Management                               | 1-21 |

| iHawk Model HQ265                                     | 1-22 |

| Specifications                                        | 1-22 |

| PCI Bus and Slot Layout                               | 1-22 |

| IRQ Priority Management                               | 1-23 |

| iHawk Model HQ067                                     | 1-24 |

| Specifications                                        | 1-24 |

| PCI Bus and Slot Layout | 1-24 |

|-------------------------|------|

| IRQ Priority Management | 1-25 |

| iHawk Model HQ047       | 1-26 |

| Specifications          | 1-26 |

| PCI Bus and Slot Layout | 1-26 |

| IRQ Priority Management | 1-27 |

# 2 **Configuration Recommendations**

This chapter provides PCI board placement recommendations for iHawk models.

The tables in this chapter are provided as an EXAMPLE ONLY in order to illustrate concepts discussed in Chapter 1 and Chapter 3.

# How to Use the IRQ Priority Management Tables

This section explains how to understand and utilize the information provided in the IRQ Priority Management tables in this chapter for iHawk models.

## **Quick Reference**

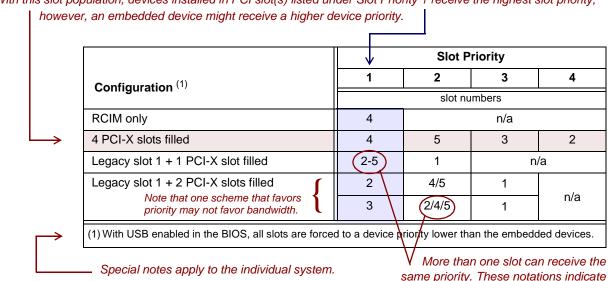

With this slot population, devices installed in PCI slot(s) listed under Slot Priority 1 receive the highest slot priority;

## Slot Priority vs. Device Priority vs. System Priority

The IRQ Priority Management tables represent the priority ranking of the physical PCI adapter slots without regard to embedded devices. Embedded devices may be assigned priorities that fall above or below a given physical slot. Because of this, we use the terms "slot priority," "device priority" and "system priority."

"slots 2 through 5" and "slots 2, 4 and 5."

| slot priority   | includes all maskable hardware interrupts belonging only to PCI cards installed in the system. |

|-----------------|------------------------------------------------------------------------------------------------|

| device priority | includes all maskable hardware interrupts: physical slots and embedded devices.                |

| system priority | includes all maskable and non-maskable hardware interrupts                                     |

As an example, the following table presents a hypothetical system.

| Device        | Device Priority | Slot Priority |  |

|---------------|-----------------|---------------|--|

| Embedded NIC2 | 1               | n/a           |  |

| RCIM card     | 2               | 1             |  |

| Embedded NIC1 | 3               | n/a           |  |

| PCI card A    | 4               | 2             |  |

| PCI card B    | 5               | 3             |  |

| PCI card C    | 6               | 4             |  |

| Embedded SCSI | 7               | n/a           |  |

On this system, the RCIM has the highest slot priority, but receives device priority 2 behind the Embedded NIC2. If NIC2 is disabled in the BIOS, the RCIM will then receive the highest device priority. If this NIC2 had been the only ethernet controller in the system, disabling it in the BIOS and installing another NIC in a PCI slot with a slot priority 2 or lower would assign the RCIM as device priority 1 and still retain the NIC2 but with a lower device priority. Use **lsirg(8)** to view the device priority assignments (see Chapter 3 or the man page).

In addition to the PCI devices and embedded devices competing for hardware priorities in the system, there are non-maskable hardware interrupts. In a display of /proc/interrupts, everything listed in the bottom section starting with NMI represents a non-maskable hardware interrupt; for example:

| \$ cat | /proc/inte | errupts |         |         |                          |

|--------|------------|---------|---------|---------|--------------------------|

|        | CPU0       | CPU1    | CPU2    | CPU3    |                          |

| 0:     | 51         | 0       | 2448698 | 0       | IO-APIC-edge timer       |

| 3:     | 0          | 0       | 0       | 0       | IO-APIC-edge KGDB-stub   |

| 4:     | 284        | 0       | 0       | 0       | IO-APIC-edge serial      |

| 9:     | 0          | 0       | 0       | 0       | IO-APIC-level acpi       |

| 14:    | 0          | 0       | 21      | 1       | IO-APIC-edge ide0        |

| 50:    | 16943      | 0       | 0       | 0       | IO-APIC-level eth0       |

| 177:   | 0          | 0       | 0       | 0       | IO-APIC-level uhci_hcd   |

| 185:   | 0          | 0       | 0       | 0       | IO-APIC-level uhci_hcd   |

| 193:   | 0          | 0       | 0       | 0       | IO-APIC-level uhci_hcd   |

| 201:   | 0          | 0       | 0       | 16      | IO-APIC-level ehci_hcd   |

| 209:   | 29         | 0       | 0       | 0       | IO-APIC-level ioc0       |

| 217:   | 0          | 3861    | 0       | 0       | IO-APIC-level ioc1       |

| 225:   | 0          | 0       | 0       | 0       | IO-APIC-level btp        |

| 233:   | 0          | 0       | 0       | 0       | IO-APIC-level rcim       |

|        |            |         |         |         |                          |

| NMI:   | 285        | 265     | 194     | 107     | Non-maskable interrupts  |

| LOC:   | 2448418    | 2448383 | 2448431 | 2448353 | Local interrupts         |

| RES:   | 93         | 77      | 81      | 106     | Rescheduling interrupts  |

| CAL:   | 112        | 113     | 116     | 58      | function call interrupts |

| TLB:   | 95         | 151     | 97      | 99      | TLB shootdowns           |

| TRM:   | 0          | 0       | 0       | 0       | Thermal event interrupts |

| SPU: | 0 | 0 | 0 | 0 | Spurious interrupts |

|------|---|---|---|---|---------------------|

| ERR: | 0 | 0 | 0 | 0 | Error interrupts    |

| MIS: | 0 | 0 | 0 | 0 | APIC errata fixups  |

Non-maskable interrupts are not configurable and will always have higher system priority over maskable interrupts.

# Installing Add-on Cards

The diagrams below show the most common slots found on iHawk systems. Use these diagrams as a guide to find the appropriate slot for adding cards to your system.

| 64-bit 133/100/66/33 MHz PCI/PCI-X Slot — 3.3 volts |  |

|-----------------------------------------------------|--|

|                                                     |  |

| 64-bit 33 MHz PCI Slot — 5 volts                    |  |

|                                                     |  |

| 32-bit 33 MHz PCI Slot — 3.3 volts                  |  |

|                                                     |  |

| 32-bit 33 MHz PCI Slot — 5 volts                    |  |

|                                                     |  |

| PCI Express x16 slot                                |  |

|                                                     |  |

Insert the card firmly into the appropriate slot. Do not force the card into the slot. If the card does not seat properly, try another slot or return the faulty card.

# **iHawk Configurations**

In the rest of this chapter, the following information is given for each iHawk model:

- **Specifications** provides the iHawk model number, manufacturer, processor type, number and types of PCI slots, number of PCI buses and a list of the embedded devices.

- **PCI Bus and Slot Layout** provides PCI slot/bus relationships, bus speed/bandwith, slot voltages and PCI bus lengths.

Note that you may find differences between spec sheets, diagrams printed on the case of your system and the contents of these tables. Use the lsirg(8) and lspci(8) tools together with this information.

• **IRQ Priority Management** provides an easy-to-read table for determining which slots to place boards in order to achieve the best possible performance based on how the system prioritizes and services interrupt requests.

## **Specifications**

| Manufacturer/Model        | Newisys® 4300                                                 |

|---------------------------|---------------------------------------------------------------|

| Processor                 | AMD Opteron™                                                  |

| Total number of PCI slots | 7                                                             |

| PCI/PCI-X                 | 7                                                             |

| PCI Express               | 0                                                             |

| Hot-plugs                 | 4                                                             |

| Number of PCI buses       | 6                                                             |

| Embedded devices          | 2 Broadcom Tigon3 BCM95703A30 Gigabit<br>Ethernet controllers |

|                           | 1 LSI Logic 53C1030 Fusion-MPT U320 SCSI<br>controller        |

|                           | 1 AMD8111 IDE controller                                      |

|                           | 1 SVGA Trident Blade3D controller                             |

|                           | 2 AMD8111 USB controllers                                     |

## **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HR430 system. The slots are numbered on the system case.

| Slot<br>Number                                                                                                                       | PCI Type       | Voltage | Maximum<br>PCI Bus<br>Speed | PCI Bus<br>Length  | Shares PCI<br>bus with |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|-----------------------------|--------------------|------------------------|

| 1 <sup>(1)</sup>                                                                                                                     | PCI            | 3.3     | 66MHz                       | half-length 64-bit | embedded devices       |

| 2                                                                                                                                    | PCI-X          | 3.3     | 100MHz                      | half-length 64-bit | slot 3                 |

| 3                                                                                                                                    | PCI-X          | 3.3     | 100MHz                      | half-length 64-bit | slot 2                 |

| 4                                                                                                                                    | PCI-X hot-plug | 3.3     | 133MHz                      | full-length 64-bit | not shared             |

| 5                                                                                                                                    | PCI-X hot-plug | 3.3     | 133MHz                      | full-length 64-bit | not shared             |

| 6                                                                                                                                    | PCI-X hot-plug | 3.3     | 133MHz                      | full-length 64-bit | not shared             |

| 7                                                                                                                                    | PCI-X hot-plug | 3.3     | 133MHz                      | full-length 64-bit | not shared             |

| (1) Embedded devices are slowed to the speed of the board installed in slot 1. Use slot 1 only if no other<br>options are available. |                |         |                             |                    |                        |

The table below shows a variety of configuration options on the iHawk HR430 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in the slot receiving Priority 1.

|                                                                                                                                                                                                                                                                                                      |         | Slot Priority |     |           |       |   |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|-----|-----------|-------|---|-----|

| Configuration <sup>(1) (2) (3)</sup>                                                                                                                                                                                                                                                                 | 1       | 2             | 3   | 4         | 5     | 6 | 7   |

|                                                                                                                                                                                                                                                                                                      |         |               | slo | ot numb   | ers   |   |     |

| RCIM only                                                                                                                                                                                                                                                                                            | 5       |               |     | n         | /a    |   |     |

| Only 64-bit PCI-X 133 MHz slots filled<br>(USB on or off)                                                                                                                                                                                                                                            | 5       | 4             | 7   | 6         | 6 n/a |   |     |

| Only 64-bit PCI-X 100 MHz slots filled<br>(USB on or off)                                                                                                                                                                                                                                            | 3 2 n/a |               |     |           |       |   |     |

| 5 64-bit PCI-X slots filled (USB off)                                                                                                                                                                                                                                                                |         | 4             | 7   | 6 3/2 n/a |       |   |     |

| All 64-bit PCI-X slots filled (USB off)                                                                                                                                                                                                                                                              |         | 7             | 6   | 3         | 2     | 5 | n/a |

| All slots filled (USB off)                                                                                                                                                                                                                                                                           | 7       | 4             | 3   | 2         | 1     | 5 | 6   |

| Legacy slot 1 + 5 PCI-X slots filled<br>(USB off)                                                                                                                                                                                                                                                    |         | 7             | 6   | 3/2       | 1     | 5 | n/a |

| Legacy slot 1 + all PCI-X 133 MHz slots<br>filled (USB off)                                                                                                                                                                                                                                          |         | 4             | 7   | 6         | 1     | n | /a  |

| Legacy slot 1+ all PCI-X 100 MHz slots<br>filled (USB on or off)     3     2     1     n/a                                                                                                                                                                                                           |         |               |     |           |       |   |     |

| <ul> <li>(1) IRQ assignments are easier to manage with USB disabled in the BIOS. Disable USB if not needed.</li> <li>(2) IRQ settings cannot be manually controlled in the BIOS on this system.</li> <li>(3) Embedded ethernet controllers cannot be disabled in the BIOS on this system.</li> </ul> |         |               |     |           |       |   |     |

## **Specifications**

| Manufacturer/Model        | Newisys® 2100                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Processor                 | AMD Opteron™                                                                                                                                                                                                                        |  |  |  |  |

| Total number of PCI slots | 2                                                                                                                                                                                                                                   |  |  |  |  |

| PCI/PCI-X                 | 2                                                                                                                                                                                                                                   |  |  |  |  |

| PCI Express               | 0                                                                                                                                                                                                                                   |  |  |  |  |

| Hot-plugs                 | 0                                                                                                                                                                                                                                   |  |  |  |  |

| Number of PCI buses       | 2                                                                                                                                                                                                                                   |  |  |  |  |

| Embedded devices          | <ol> <li>Broadcom Tigon3 BCM5703x Gigabit Ethernet<br/>controllers</li> <li>LSI Logic 53C1030 Fusion-MPT Dual Channel<br/>U320 SCSI controller</li> <li>SVGA Trident Blade3D controller</li> <li>AMD8111 USB controllers</li> </ol> |  |  |  |  |

## **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HR210 system. The slots are numbered on the main board next to each slot.

| Slot<br>Number<br>(1)                                                                                          | РСІ Туре | Voltage | Maximum<br>PCI Bus<br>Speed | PCI Bus Length     | Shares PCI<br>bus with |  |

|----------------------------------------------------------------------------------------------------------------|----------|---------|-----------------------------|--------------------|------------------------|--|

| 1                                                                                                              | PCI-X    | 3.3     | 66 MHz                      | full-length 64-bit | not shared             |  |

| 2                                                                                                              | PCI-X    | 3.3     | 133 MHz                     | full-length 64-bit | not shared             |  |

| (1) These slot numbers reflect the numbering provided on the hardware. The BIOS uses "slot 0" and<br>"slot 1." |          |         |                             |                    |                        |  |

The table below shows a variety of configuration options on the iHawk HR210 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in the slot receiving Priority 1.

|                                                                                                                                                                             | Slot Priority |     |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|--|--|

| Configuration <sup>(1)</sup>                                                                                                                                                | 1             | 2   |  |  |

| Computation                                                                                                                                                                 | slot numbers  |     |  |  |

| RCIM only                                                                                                                                                                   | 2/1           | n/a |  |  |

| 1 slot filled                                                                                                                                                               | 2/1           | n/a |  |  |

| 2 slots filled                                                                                                                                                              | 2             | 1   |  |  |

| (1)Managing IRQ priorities is usually more straightforward with<br>especially true with multi-IRQ boards, which may not assign<br>order (e.g., device priority 2, 3, 4, 10) |               |     |  |  |

## **Specifications**

| Manufacturer/Model        | Dell™ PowerEdge™ 6850                                                                                                                                                                                                                                                                                       |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Processor                 | Intel® Xeon™                                                                                                                                                                                                                                                                                                |  |  |  |

| Total number of PCI slots | 7                                                                                                                                                                                                                                                                                                           |  |  |  |

| PCI/PCI-X                 | 3                                                                                                                                                                                                                                                                                                           |  |  |  |

| PCI Express               | 4                                                                                                                                                                                                                                                                                                           |  |  |  |

| Hot-plugs                 | 4                                                                                                                                                                                                                                                                                                           |  |  |  |

| Number of PCI buses       | 6                                                                                                                                                                                                                                                                                                           |  |  |  |

| Embedded devices          | <ol> <li>VGA ATI Radeon/16MB SRAM</li> <li>Broadcom BCM5704 Dual Gigabit Ethernet controllers</li> <li>LSI Logic 53C1030 Dual Integrated PCI Ultra320 LVD<br/>SCSI controller</li> <li>Intel 82801EB/ER (ICH5/ICH5R) USB2 EHCI<br/>controller</li> <li>Intel 82801EB/ER (ICH5/ICH5R) USB UHCI #1</li> </ol> |  |  |  |

## **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HQ685 system.

| Slot<br>Number                                                                                          | Bus<br>Number | РСІ Туре                | Voltage | Maximum<br>PCI Bus<br>Speed | PCI Bus Length     |

|---------------------------------------------------------------------------------------------------------|---------------|-------------------------|---------|-----------------------------|--------------------|

| 1                                                                                                       | 1             | PCI Express<br>hot-plug | 3.3     | 40 Gbps                     | x8 lane width      |

| 2                                                                                                       | 2             | PCI-X                   | 3.3     | 133 MHz                     | full-length 64-bit |

| 3                                                                                                       | 3             | PCI Express<br>hot-plug | 3.3     | 20 Gbps                     | x4 lane width      |

| 4                                                                                                       | 4             | PCI Express<br>hot-plug | 3.3     | 20 Gbps                     | x4 lane width      |

| 5                                                                                                       | 5             | PCI Express<br>hot-plug | 3.3     | 20 Gbps                     | x4 lane width      |

| 6                                                                                                       | 6             | PCI-X                   | 3.3     | 100 MHz                     | full-length 64-bit |

| 7                                                                                                       | 6             | PCI-X                   | 3.3     | 100 MHz                     | full-length 64-bit |

| (1) Embedded USB, SCSI and Ethernet cannot be disabled unless a corresponding PCI adapter is installed. |               |                         |         |                             |                    |

The table below shows a variety of configuration options on the iHawk HQ685 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in the slot receiving Priority 1.

|                                                                                                                                      |       | Slot Priority <sup>(1)</sup> |     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|-----|--|--|

| Configuration                                                                                                                        | 1     | 2                            | 3   |  |  |

| Computation                                                                                                                          |       | slot numbers                 |     |  |  |

| RCIM only                                                                                                                            | 6/7/2 | n                            | n/a |  |  |

| 1 PCI-X slot filled                                                                                                                  | 6/7/2 | n/a                          |     |  |  |

| 2 PCI-X slots filled                                                                                                                 | 6     | 7                            |     |  |  |

|                                                                                                                                      | 2     | 6/7                          | n/a |  |  |

| 3 PCI-X slots filled                                                                                                                 | 2     | 7                            | 6   |  |  |

| (1)PCI Express cards receive priorities in the mid level range and have less impact on PCI-X slot priorities than other PCI-X cards. |       |                              |     |  |  |

## **Specifications**

| Manufacturer/Model        | Dell™ PowerEdge™ 6800                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Processor                 | Intel® Xeon™                                                                                                                                                                                                                                                                                                 |  |  |  |

| Total number of PCI slots | 7                                                                                                                                                                                                                                                                                                            |  |  |  |

| PCI/PCI-X                 | 3                                                                                                                                                                                                                                                                                                            |  |  |  |

| PCI Express               | 4                                                                                                                                                                                                                                                                                                            |  |  |  |

| Hot-plugs                 | 0                                                                                                                                                                                                                                                                                                            |  |  |  |

| Number of PCI buses       | 6                                                                                                                                                                                                                                                                                                            |  |  |  |

| Embedded devices          | <ol> <li>VGA ATI Radeon/ 16MB SRAM</li> <li>Broadcom BCM5704 Dual Gigabit Ethernet controllers</li> <li>LSI Logic 53C1030 Dual Integrated PCI Ultra320 LVD<br/>SCSI controller</li> <li>Intel 82801EB/ER (ICH5/ICH5R) USB2 EHCI<br/>controller</li> <li>Intel 82801EB/ER (ICH5/ICH5R) USB UHCI #1</li> </ol> |  |  |  |

## **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HQ680 system.

| Slot<br>Number | Bus<br>Number | PCI Type            | Voltage        | Maximum<br>PCI Bus<br>Speed | PCI Bus Length       |

|----------------|---------------|---------------------|----------------|-----------------------------|----------------------|

| 1              | 1             | PCI Express         | 3.3            | 40 Gbps                     | x8 lane width        |

| 2              | 2             | PCI-X               | 3.3            | 133 MHz                     | full-length 64-bit   |

| 3              | 3             | PCI Express         | 3.3            | 20 Gbps                     | x4 lane width        |

| 4              | 4 4 PCI E     |                     | 3.3            | 20 Gbps                     | x4 lane width        |

| 5              | 5             | PCI Express         | 3.3            | 20 Gbps                     | x4 lane width        |

| 6              | 6             | PCI-X               | 3.3            | 100 MHz                     | full-length 64-bit   |

| 7              | 6             | PCI-X               | 3.3            | 100 MHz                     | full-length 64-bit   |

| (1) Embedd     | ed USB. SCS   | I and Ethernet cann | ot be disabled | unless a correspo           | nding PCI adapter is |

(1) Embedded USB, SCSI and Ethernet cannot be disabled unless a corresponding PCI adapter is installed.

The table below shows a variety of configuration options on the iHawk HQ680 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in the slot receiving Priority 1.

|                                                                                           |                        | Slot Priority <sup>(1)</sup> | )         |  |

|-------------------------------------------------------------------------------------------|------------------------|------------------------------|-----------|--|

| Configuration                                                                             | 1                      | 2                            | 3         |  |

| Computation                                                                               |                        | slot numbers                 |           |  |

| RCIM only                                                                                 | 6/7/2                  | n,                           | /a        |  |

| 1 PCI-X slot filled                                                                       | 6/7/2                  | n/a                          |           |  |

| 2 PCI-X slots filled                                                                      | 6                      | 7                            | 2/2       |  |

|                                                                                           | 2                      | 6/7                          | n/a       |  |

| 3 PCI-X slots filled                                                                      | 2                      | 7                            | 6         |  |

| (1) PCI Express cards receive priorities in the mid<br>priorities than other PCI-X cards. | l level range and have | e less impact on P           | CI-X slot |  |

#### **Specifications**

| Manufacturer/Model        | Dell™ PowerEdge™ 6650                                                                                                        |  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Processor                 | Intel® Xeon™                                                                                                                 |  |  |  |  |  |

| Total number of PCI slots | 8                                                                                                                            |  |  |  |  |  |

| PCI/PCI-X                 | 8                                                                                                                            |  |  |  |  |  |

| PCI Express               | 0                                                                                                                            |  |  |  |  |  |

| Hot-plugs                 | 0                                                                                                                            |  |  |  |  |  |

| Number of PCI buses       | 6                                                                                                                            |  |  |  |  |  |

| Embedded devices          | <ol> <li>Broadcom Tigon 3 BCM 5700 Gigabit Ethernet<br/>controllers</li> <li>Adaptec AIC7892 U160 SCSI controller</li> </ol> |  |  |  |  |  |

|                           | 1 Serverworks CSB5 IDE controller                                                                                            |  |  |  |  |  |

|                           | 1 Serverworks OSB4/CSB5 OHCI USB controller                                                                                  |  |  |  |  |  |

## **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HQ665 system. Slot numbers are provided on the main board adjacent to each PCI slot and on the outside of the case.

| Slot<br>Number   | Bus<br>Number | РСІ Туре             | Voltage | Maximum<br>PCI Bus<br>Speed | PCI Bus Length     |

|------------------|---------------|----------------------|---------|-----------------------------|--------------------|

| 1 <sup>(1)</sup> | 1             | PCI 2.2              | 5       | 33 MHz                      | half-length 32-bit |

| 2 (2)            | 3             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 3 (2)            | 3             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 4                | 4             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 5                | 4             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 6                | 5             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 7                | 5             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| 8                | 6             | PCI-X                | 3.3     | 100 MHz                     | full-length 64-bit |

| (1) Remote       | access cards  | must be installed in | slot 1. |                             |                    |

(1) Remote access cards must be installed in slot 1.

(2) RAID controllers for internal hard drives must be installed in slot 2 or slot 3.

The table below shows a variety of configuration options on the iHawk HQ665 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in a slot receiving Priority 1.

|                                               | Slot Priority <sup>(1)</sup> |     |     |         |        |         |                                                                           |     |  |  |

|-----------------------------------------------|------------------------------|-----|-----|---------|--------|---------|---------------------------------------------------------------------------|-----|--|--|

| Configuration                                 | 1                            | 2   | 3   | 4       | 5      | 6       | 7                                                                         | 8   |  |  |

| <b>J</b>                                      |                              |     |     | slot nu | Imbers |         | n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>8 5<br>n/a<br>n/a<br>8 5<br>n/a<br>8 5 |     |  |  |

| RCIM only                                     | 8-4                          |     |     |         | n/a    |         |                                                                           |     |  |  |

| 1 PCI-X slot filled                           | 8-4                          |     |     |         | n/a    |         |                                                                           |     |  |  |

| 2 PCI-X slots filled                          | 8 7/6                        |     |     |         |        |         |                                                                           |     |  |  |

|                                               | 7                            | 6   |     |         |        | 1-      |                                                                           |     |  |  |

|                                               | 5                            | 4   |     |         | n      | /a      |                                                                           |     |  |  |

|                                               | 3                            | 2   |     |         |        |         |                                                                           |     |  |  |

| 3 PCI-X slots filled                          | 7                            | 8   | 6   |         |        |         |                                                                           |     |  |  |

|                                               | 5                            | 4   | 3/2 | -       |        | n/a     |                                                                           |     |  |  |

| 4 PCI-X slots filled                          | 7                            | 8   | 5/4 | 6       |        |         |                                                                           |     |  |  |

|                                               | 7                            | 8   | 6   | 3/2     |        | n       | /a                                                                        |     |  |  |

|                                               | 5                            | 4   | 3   | 2       |        |         |                                                                           |     |  |  |

| 5 PCI-X slots filled                          | 8                            | 5   | 4   | 6       | 7      |         |                                                                           |     |  |  |

|                                               | 7                            | 6   | 3   | 2       | 8      | -       | n/a                                                                       |     |  |  |

|                                               | 8                            | 5/4 | 6   | 3/2     | 7      | -       |                                                                           |     |  |  |

| 6 PCI-X slots filled                          | 5                            | 4   | 6   | 3/2     | 7      | 8 n/a   |                                                                           |     |  |  |

| All PCI-X slots filled                        | 4                            | 6   | 3   | 2       | 7      | 8 5 n/a |                                                                           |     |  |  |

| Legacy slot 1 + 1 PCI-X slot                  | 8-2                          | 1   |     | 1       | n      | /a      | 'a                                                                        |     |  |  |

| Legacy slot 1 + 2 PCI-X slots                 | 7                            | 8   | 1   |         |        |         |                                                                           |     |  |  |

|                                               | 8/7                          | 6   | 1   | n/a     |        |         |                                                                           |     |  |  |

|                                               | 5/4                          | 3/2 | 1   |         |        |         |                                                                           |     |  |  |

| Legacy slot 1 + 3 PCI-X slots                 | 7                            | 8   | 6   | 1       |        |         | 1                                                                         |     |  |  |

| 0                                             | 5                            | 4   | 3/2 | 1       |        | n       | /a                                                                        |     |  |  |

| Legacy slot 1 + 4 PCI-X slots                 | 8                            | 5/4 | 6   | 1       | 7      |         |                                                                           |     |  |  |

|                                               | 8                            | 6   | 3/2 | 1       | 7      | 1       | n/a                                                                       |     |  |  |

|                                               | 4                            | 3   | 2   | 1       | 5      | •       |                                                                           |     |  |  |

| Legacy slot 1 + 5 PCI-X slots                 | 5                            | 4   | 6   | 1       | 7      | 8       |                                                                           |     |  |  |

|                                               | 5                            | 6   | 3   | 1       | 7      | 8       | n                                                                         | /a  |  |  |

|                                               | 6                            | 3   | 2   | 1       | 7      | 8       | 1                                                                         |     |  |  |

| Legacy slot 1 + 6 PCI-X slots                 | 4                            | 6   | 3/2 | 1       | 7      | 8       | 5                                                                         |     |  |  |

| <u>, , , , , , , , , , , , , , , , , , , </u> | 6                            | 3   | 2   | 1       | 7      | 8       | 5/4                                                                       | n/a |  |  |

| Legacy slot 1 + 7 PCI-X slots                 | 6                            | 3   | 2   | 1       | 7      | 8       | 5                                                                         | 4   |  |  |

#### **Specifications**

| Manufacturer/Model        | Dell™ PowerEdge™ 6600                                       |  |  |  |  |  |  |

|---------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| Processor                 | Intel® Xeon™                                                |  |  |  |  |  |  |

| Total number of PCI slots | 11                                                          |  |  |  |  |  |  |

| PCI/PCI-X                 | 11                                                          |  |  |  |  |  |  |

| PCI Express               | 0                                                           |  |  |  |  |  |  |

| Hot-plugs                 | 0                                                           |  |  |  |  |  |  |

| Number of PCI buses       | 7                                                           |  |  |  |  |  |  |

| Embedded devices          | 2 Broadcom Tigon3 BCM9500A6 Gigabit Ethernet<br>controllers |  |  |  |  |  |  |

|                           | 2 Adaptec AIC7892 SCSI controllers                          |  |  |  |  |  |  |

|                           | 1 Serverworks CSB5 IDE controller                           |  |  |  |  |  |  |

|                           | 1 Serverworks OSB4/CSB5 OHCI USB controller                 |  |  |  |  |  |  |

#### **PCI Bus and Slot Layout**

The table below provides details of the PCI slots and buses found on the iHawk HQ660 system. Slot numbers are marked on the main board adjacent to each PCI slot and on the outside of the case.

| 2 <sup>(2)</sup> 3         PCI-X         3.3         100 MHz         full-length 64-b           3 <sup>(2)</sup> 3         PCI-X         3.3         100 MHz         full-length 64-b           4         4         PCI-X         3.3         100 MHz         full-length 64-b           5         4         PCI-X         3.3         100 MHz         full-length 64-b           6         5         PCI-X         3.3         100 MHz         full-length 64-b           7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b | Slot<br>Number   | Bus<br>Number | РСІ Туре | Voltage | Maximum<br>PCI Bus<br>Speed | PCI Bus Length     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|----------|---------|-----------------------------|--------------------|

| 3 (2)         3         PCI-X         3.3         100 MHz         full-length 64-b           4         4         PCI-X         3.3         100 MHz         full-length 64-b           5         4         PCI-X         3.3         100 MHz         full-length 64-b           6         5         PCI-X         3.3         100 MHz         full-length 64-b           7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                    | 1 <sup>(1)</sup> | 1             | PCI 2.2  | 5       | 33 MHz                      | half-length 32-bit |

| 4         4         PCI-X         3.3         100 MHz         full-length 64-b           5         4         PCI-X         3.3         100 MHz         full-length 64-b           6         5         PCI-X         3.3         100 MHz         full-length 64-b           7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                 | 2 <sup>(2)</sup> | 3             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 5         4         PCI-X         3.3         100 MHz         full-length 64-b           6         5         PCI-X         3.3         100 MHz         full-length 64-b           7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                                                                                                          | 3 (2)            | 3             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 6         5         PCI-X         3.3         100 MHz         full-length 64-b           7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                   | 4                | 4             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 7         5         PCI-X         3.3         100 MHz         full-length 64-b           8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                | 4             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 8         6         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                | 5             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                | 5             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 9 6 PCI-X 3.3 100 MHz full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                | 6             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                | 6             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 10 7 PCI-X 3.3 100 MHz full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10               | 7             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

| 11         7         PCI-X         3.3         100 MHz         full-length 64-b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11               | 7             | PCI-X    | 3.3     | 100 MHz                     | full-length 64-bit |

(2) RAID controllers for internal hard drives must be installed in slot 2 or slot 3.

The table below shows a variety of configuration options on the iHawk HQ660 system and the corresponding IRQ priority levels that are assigned to each slot.

The device requiring the highest IRQ priority level (usually the RCIM) should be located in the slot receiving Priority 1.

|                                                                     |       |           |     |     | SI  | ot Prior  | ity         |     | lot Priority |     |     |  |

|---------------------------------------------------------------------|-------|-----------|-----|-----|-----|-----------|-------------|-----|--------------|-----|-----|--|

| Configuration                                                       | 1     | 2         | 3   | 4   | 5   | 6         | 7           | 8   | 9            | 10  | 11  |  |

|                                                                     |       | 1         |     |     | slo | ot numbe  | ers         |     |              |     |     |  |

| RCIM only                                                           | 11/10 | 11/10 n/a |     |     |     |           |             |     |              |     |     |  |

| 1 PCI-X slot filled on separate bus<br>(NIC2 on/off)                | 11/10 |           |     |     |     | n/        | ′a          |     |              |     |     |  |

| 2 PCI-X slots filled on separate<br>buses (NIC2 on/off)             | 9/8   | 11/10     |     |     |     |           | n/a         |     |              |     |     |  |

| 3 PCI-X slots filled on separate<br>buses (NIC2 on/off)             | 9/8   | 11/10     | 7/6 |     |     |           | n           | /a  |              |     |     |  |

| 4 PCI-X slots filled on separate<br>buses (NIC2 on)                 | 11/10 | 7/6       | 5/4 | 9/8 |     |           |             | n/a |              |     |     |  |

| 4 PCI-X slots filled on separate<br>buses (NIC2 off)                | 9/8   | 11/10     | 5/4 | 7/6 |     |           |             | n/a |              |     |     |  |